【工程师分享】ZCU106的超低延时gstreamer编解码命令

judy 在 周日, 04/25/2021 - 15:53 提交

Xilinx提供超低延时编解码方案,在ZCU106单板上可以验证。文档MPSoC VCU TRD 2020.2 Low Latency NV16 提供了详细命令。下面的命令,能表现得更加稳定。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

Xilinx提供超低延时编解码方案,在ZCU106单板上可以验证。文档MPSoC VCU TRD 2020.2 Low Latency NV16 提供了详细命令。下面的命令,能表现得更加稳定。

在工业现场的设备运维管理,从第一代人工观测,到第二代的定期仪器检测,再到第三代的实时状态检测,直至现在过度到了利用云计算,大数据,人工智能技术主动的预测设备运营状态,根据各传感器信息和设备运行数据提前预测设备的更新和维护。

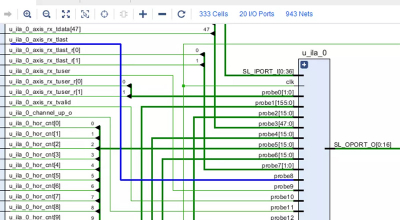

在 AXI 基础第 6 讲 - Vitis HLS 中的 AXI4-Lite 简介中,使用 C 语言在 HLS 中创建包含 AXI4-Lite 接口的 IP。在本篇博文中,我们将学习如何导出 IP 以供在 Vivado Design Suite 中使用、如何将其连接到其它 IP 核与处理器以及如何在板上运行工程。

ECO 指的是 Engineering Change Order ,即工程变更指令。目的是为了在设计的后期,快速灵活地做小范围修改,从而尽可能的保持已经验证的功能和时序。ECO 是从 IC 设计领域继承而来,Vivado上 的 ECO 便相当于 ISE 上的 FPGA Editor。

ZU+MPSOC器件在汽车电子、工业控制、机器视觉、智能安防、智慧城市等行业中已经有着广泛的应用,三年前在做一个ZCU106开发板的TRD(Target Reference Design)向用户自研板卡移植HDMI设计时,遇到了一些问题,我翻出之前的笔记整理成文,与大家分享。

本示例工程中我们会在 TensorFlow2 下使用 Keras API 创建一个自定义 CNN 网络,在 Vitis-AI 1.3 环境下编译成 Xilinx DPU 上运行的模型文件,并在 Xilinx zynqMP 上部署运行。该示例工程应在 Vitis-AI1.3 Docker,vitis-ai-tensorflow2conda 环境中运行。

时序约束中的 set_input_delay/set_output_delay 约束一直是一个难点,无论是概念、约束值的计算,还是最终的路径分析,每一次都要费一番脑子。Vivado为方便用户创建输入输出接口的约束,整理出了一套非常实用的InputDelay/Output Delay Constraints Language Templates。

百度大脑EdgeBoard AI计算盒/计算卡系百度与米尔联合推出的一款高性能,高可靠性的AI计算盒/计算卡。该产品基于Xilinx Zynq UltraScale+ MPSoC 系列 FPGA可伸缩计算架构,可支持二次开发,支持高精度模型/多模型部署

前段时间看到Xilinx发布了新的差异化ZYNQ Ultrascale+ MPSoC ZU1和Artix Ultrascale+FPGA,熊猫君趁着国家假日有点时间,随便瞎聊一下。本次发布的新产品均采用16nm的工艺,可选封装有0.5mm焊盘间距紧凑型的InFo,最小封装尺寸只有15mm*9.5mm,这种封装类型可以缩短信号互联,有利于提高信号完整性

本文介绍了一种基于VPX架构的高速宽带数据通信平台,平台的核心是机载和地面收发信机,收发信机内各功能板卡的主要控制器是FPGA。发射端对信息序列进行打包、信道编码、交织和调制;接收端对信号进行解调、解交织、解码、同步等操作。还原后的信息上传至上位机进行分析。