FMCW激光雷达原型验证和测试

judy 在 周二, 06/08/2021 - 15:52 提交

调频连续波(FMCW)光雷达的原型验证和测试面临着许多挑战。接下来让我们一起探讨,对这些挑战进行分解,使其变得可管理且可付诸行动,并学习有关如何逐步克服组件级到系统级测试挑战的实用指南。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

调频连续波(FMCW)光雷达的原型验证和测试面临着许多挑战。接下来让我们一起探讨,对这些挑战进行分解,使其变得可管理且可付诸行动,并学习有关如何逐步克服组件级到系统级测试挑战的实用指南。

Linux是现在最流行的操作系统,含有大量的源代码。Xilinx 2020.1使用的Linux 5.4,含有大约67430个文件。大部分文件没有被使用到。分析Linux源代码的代码实现时,经常查找函数或者数据结构定义。如果分析所有文件,既消耗软件查找时间;也会找到多个定义,增加理解代码的难度

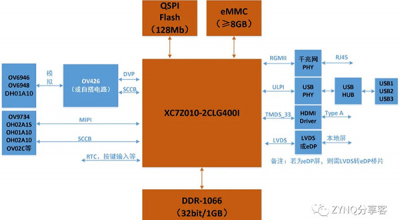

这一次,熊猫君分享一个内窥镜的技术实现方案。内窥镜的方案很多:主处理器有用专用ASIC的,比如日、台、韩的相机ASIC;有用专用CPU的,比如海思、瑞星微和君正等。熊猫君的这个是基于Xilinx ZYNQ的低成本方案。

每个 RPU 处理器都有 1 个 DBGDSAR 寄存器,其中包含其 CoreSight ROM 表的偏移地址。但是,读取 RPU 的 DBGDSAR 寄存器会返回以下不正确的偏移值:

Vivado可以导出脚本,保存创建工程的相关命令和配置,并可以在需要的时候使用脚本重建Vivado工程。脚本通常只有KB级别大小,远远小于工程打包文件的大小,因此便于备份和版本管理。下面把前述脚本升级到Vivado 2020.2为例,讨论如何升级Vivado工程脚本。

在任何一致的 ACE 系统中,启用 WriteUnique/WriteLineUnique (WU/WLU) 传输事务后,如果在有一项或多项高速缓存逐出事务处于暂挂状态时尝试执行存储,那么写回无分配 (WBNA) 存储可能发生停滞。

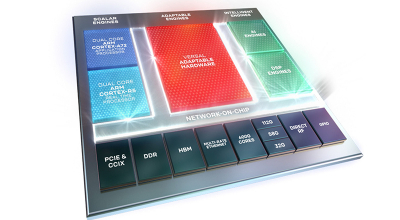

在Vitis 统一软件平台中使用Alveo系列开发板设计加速Kernel时,系统会自动为Kernel的时钟设置默认频率。以 xilinx_u200_qdma_201910_1 平台为例,在Vitis中选择平台时可以看到默认的时钟频率是300Mhz和500Mhz。

当在硬件配置中包含“大型发送卸载 (Large Send Offload)”并在缓冲区描述符中启用 LSO 功能时,GEM IP 可能通过中断状态寄存器的位 6(同样反映在发射状态寄存器的位 4 中)错误触发“amba error”中断事件

在Xilinx的ZCU102和ZCU106单板设计中,使用了管脚PS_MODE1作为外部USB Phy的复位信号。在MPSoC的文档ug1085和ug1087中,关于PS_MODE1的信息比较少。下面是更详细的描述。

Arm Cortex-R5F 处理器包含 1 个 4 输入存储缓冲器,用于对数据先进行缓冲、合并和转发,然后再使用 AXI 主接口将数据写入高速缓存或 L2 存储器系统。由于此错误,存储缓冲器可能进入所有现有写入都无法继续执行的状态。此状态可能会导致下列问题: