SOM (System-on-Module):使用 SOM 的方法和理由

judy 在 周一, 08/02/2021 - 16:39 提交

SOM (System-on-Module) 在随时可投入生产的单块印刷电路板 (PCB) 上提供嵌入式处理系统的各种核心组件,包括处理器内核、通信接口和内存模块等。有了这种模块化方法,SOM 将成为嵌入各种终端系统的理想选择,从机器人到安全摄像头,无所不包

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

SOM (System-on-Module) 在随时可投入生产的单块印刷电路板 (PCB) 上提供嵌入式处理系统的各种核心组件,包括处理器内核、通信接口和内存模块等。有了这种模块化方法,SOM 将成为嵌入各种终端系统的理想选择,从机器人到安全摄像头,无所不包

本设计咨询涵盖如下 Versal DDRMC 设计:使用对应 LPDDR4 和 x8 或 x16 DDR4 组件接口的 DQS 字节组管脚交换所生成的设计。

本文主要包含MultiBoot的功能简介、流程介绍和工程实现几个部分的讲解。

大多数FPGA程序员认为,高级工具总是发出更大的比特流,作为提高生产率的"成本"。 但事实总是如此吗?在本文中,我们展示了一个真实的例子

本篇博文将继续介绍在Vitis中把Settings信息传递到底层的Vivado。

该设计咨询涵盖如下 UltraScale+ GTH/GTY 收发器问题,即 GTPOWERGOOD 在上电后可能无法断言有效。所有 UltraScale+ GTH/GTY 收发器中均包含 *_delay_powergood.v 模块。

在Vitis完成这个过程的底层,实际调用的是Vivado。Vitis会指定默认的Vivado策略来执行综合和实现的步骤。当默认的Vivado策略无法达到预期的时序要求时,我们需要在Vivado中分析时序问题的原因, 并根据时序失败的原因调整Vivado各个步骤的选项。有时我们也需要调整Vivado各个步骤的选项做不同方向的优化。

DNN加速器的设计一直在两个方面使力:通用架构和高效性能。通用性需要自顶向下的设计,首先综合各种神经网络的算子设计一套标准的指令集,然后根据硬件平台的特点,考察计算资源,存储资源以及带宽,进行硬件的模块化设计,在指令集以及硬件的特殊结构基础上,再去构建工具链。

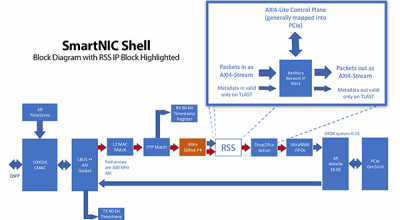

以太网技术继续向更高、更优的性能和功能水平不断迈进。万兆以太网 (GbE) 有望满足苛刻的市场需求,提升性能并仍能兼容之前的各种变型。它可以满足高性能实时系统、云计算、零延迟传输系统和高性能嵌入式计算 (HPEC) 的苛刻需求。它也是高速处理器之间和 I/O 通信的可行性选择。

在本篇博文中,我们将在“猫和狗”数据库上重复先前第 2 部分中已完成的过程,并且我们将添加一些其它内容。