基于FPGA的SmartNIC技术及其在数据中心的应用

judy 在 周五, 06/25/2021 - 14:28 提交

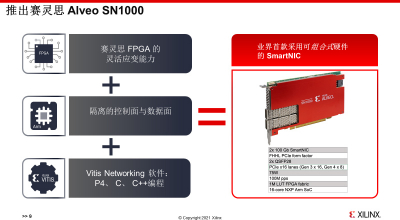

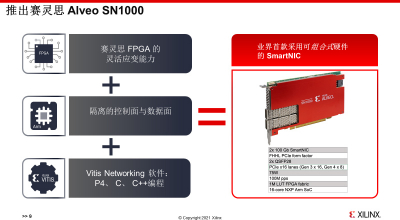

自上世纪80 年代中期首批 PC 机面市后不久,网络接口卡 (NIC) 就已经进入了市场。然而,在过去的几年里,我们看到了 SmartNIC 的兴起。什么是 SmartNIC?按照最基本的定义,SmartNIC 就是可编程NIC。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

自上世纪80 年代中期首批 PC 机面市后不久,网络接口卡 (NIC) 就已经进入了市场。然而,在过去的几年里,我们看到了 SmartNIC 的兴起。什么是 SmartNIC?按照最基本的定义,SmartNIC 就是可编程NIC。

从前,嵌入式系统的开发从硬件开始。现在,可以再加入FPGA!面对应用需求越来越复杂的物联网细分市场,以及快速迭代和成本效益的挑战,选择一种现成套件用于无线传感节点原型设计和调试,是一种兼具开发效率和成本效益的解决方案,而全面的软件环境和优化的硬件平台可加快你的开发进度。在这个一连三集的开发板小系列,我们一起来了解更多

(UG332) 即为《Spartan-3 系列配置用户指南》。在此用户指南中,并未涵盖有关从 SPI 闪存启动时,如何使用内部配置访问端口 (ICAP) 来支持在 Spartan-3AN FPGA 内运行多重启动应用的用例。我们将在本篇博文中讲解此用例。

当在硬件配置中包含“大型发送卸载 (Large Send Offload)”并在缓冲区描述符中启用 LSO 功能时,GEM IP 可能通过中断状态寄存器的位 6(同样反映在发射状态寄存器的位 4 中)错误触发“amba error”中断事件。除了误报此错误外,并未观测到任何功能性问题,且仍可继续使用 LSO 卸载功能。

如果 Arm Cortex-A72 处理器配置为向处于 UniqueClean (UC) 状态的缓存行发送逐出传输事务,那么 Cortex-A72 处理器可能返回陈旧数据并发出嗅探响应。

在 aarch32 模式下,如果执行的代码包含下面的加密指令序列,并且在执行第一条加密指令后立即断言并中断,ELR 会被记录为返回地址,产生的错误可能会导致数据损坏

MicroBlaze可以使用AXI BRAM存放数据和指令。有些客户软件很大,需要把AXI BRAM的空间做到最大。AXI BRAM底层是Block RAM或者Ultra RAM。器件的Block RAM或者Ultra RAM个数,决定了AXI BRAM的大小。

Alveo系列开发板上的平台其实是一个DFX设计的静态部分,在Vitis 统一软件平台中使用Alveo系列开发板设计加速Kernel, 最终这些Kernel的逻辑会在分布在DFX设计的动态区域。本篇将介绍如何为Kernel的逻辑做floorplan(画Pblock),人为控制Kernel逻辑的布局。

现在大规模FPGA的bitstream比较大导致板卡从上电到FPGA配置完成的时间远远超过100MS的要求,从而电脑端无法正常识别到PCIE设备。为此Xilinx的PCIE Tandem功能是专为满足PCIe设备在100ms之内枚举起来要求而设计的。

在开发一个加速程序的之前,有一个很重要的步骤:正确设计程序架构。开发人员需要明确软件应用程序中哪一部分是需要硬件加速的,并且它多少的并行量,以保证硬件加速器件(FPGA)能完美发挥其作用。本文将分为5个步骤来介绍