开发者分享 | PetaLinux 镜像调试系列-在 Vitis 中调试 ARM 可信固件和 U-boot

judy 在 周一, 05/31/2021 - 10:52 提交

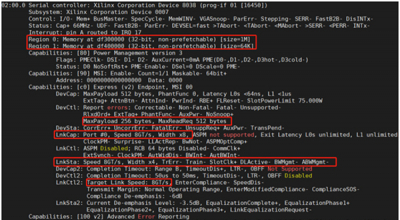

在本篇博文中,我们将探讨如何在 Vitis 中调试 Zynq UltraScale 器件启动镜像。这些启动镜像包括 ARM 可信固件 (ATF) 和 U-boot。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

在本篇博文中,我们将探讨如何在 Vitis 中调试 Zynq UltraScale 器件启动镜像。这些启动镜像包括 ARM 可信固件 (ATF) 和 U-boot。

XBERT是一个API和设计工具集,用于使用设备的配置路径零成本访问Xilinx体系结构上的片上SRAM块。XBERT API是高级别的,允许开发人员根据应用程序源代码中的逻辑内存指定类似DMA的内存内容数据传输,因此基本上适用于任何针对Xilinx设备的设计。应用程序开发人员可以广泛地访问XBERT,它隐藏了物理映射和比特流编码的底层细节。

在FPGA需要和处理器打交道时,无论是X86,还是PowerPC,以及一些嵌入式的ARM等,对外的接口常见如下表。

本答复记录旨在描述在 Versal ACAP 器件上使用物理不可克隆功能 (Physically Unclonable Function,PUF) 时,与 VCC_PMC 电源轨相关的要求。

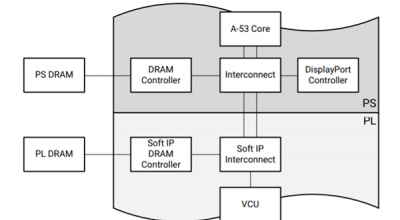

Xilinx提供超低延时编解码方案,并提供了全套软件。MPSoC Video Codec Unit提供了详细说明。其中的底层应用软件是VCU Control-Software(Ctrl-SW)。本文主要说明为Ctrl-SW增加功能,支持不同Stride/Pitch(步长)的YUV文件的编码。

在某些条件下,新负载如果复用旧器件负载的分组标识 (GID),则可能报告同步外部异常中止,原因是错误关联旧器件存储器访问所检测到的外部错误。器件负载快速解析完成,并允许后续指令执行时复用 GID。

Lower操作完成从高级算子(relay)到低级算子(TOPI)的转化。Lower开始于以下代码(src/relay/backend/graph_runtime_codegen.cc)

Xilinx提供超低延时编解码方案,并提供了全套软件。MPSoC Video Codec Unit提供了详细说明。其中的底层应用软件是VCU Control-Software(Ctrl-SW)。本文主要说明为Ctrl-SW增加输出NV12视频的功能。

OpenAMP framework支持standalone和linux环境下加载RPU的程序,但是没有u-boot下面的支持。U-boot下可以把rpu app binary加载到memory,然后用“cpu”命令启动rpu app。这个流程不是官方支持的方法,所以不在支持范围内,这里只做可行性探讨。下面是简单测试过可行的方法。

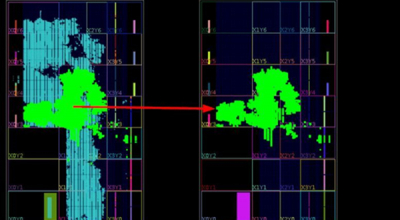

本文旨在提供一种方法,以帮助设计师判断给定模块是否能够在空裸片上达成时序收敛。 如果目标模块无法在空裸片上达成非关联 (OOC) 时序收敛,则恐难以与设计其余部分达成关联性时序收敛。设计师可从完整设计中提取目标模块、对其进行布局规划、约束,然后通过实现工具来运行这些模块,以判断是否能够独立达成时序收敛。