浅谈Ultrascale、Ultrascale+ Serdes与7 Series GTX/GTH的区别

judy 在 周四, 05/20/2021 - 10:29 提交

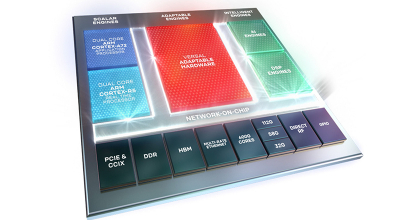

在Serdes流行之前,芯片之间的数据传输主要靠低俗串行接口和并行接口,存在诸如传输速率低、占用IO数量多、硬件连接复杂化等弊端。Serdes的出现简化了数据传输接口的硬件设计,大大提升了数据传输的速率和带宽效率。 今天我们来聊一聊7 Series、Ultrascale系列GTH与Ultrascale+ GTY的内部区别。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

在Serdes流行之前,芯片之间的数据传输主要靠低俗串行接口和并行接口,存在诸如传输速率低、占用IO数量多、硬件连接复杂化等弊端。Serdes的出现简化了数据传输接口的硬件设计,大大提升了数据传输的速率和带宽效率。 今天我们来聊一聊7 Series、Ultrascale系列GTH与Ultrascale+ GTY的内部区别。

本视频说明了如何使用 Xilinx 功耗估算器工具预测 Zynq®UltraScale +™RFSoC 的 RF 数据转换器 IP 的功耗。

人工智能发展迅速,创新步伐不断加快。然而,虽然软件行业已经成功在生产中部署了 AI,但包括汽车、工业和智能零售等在内的硬件行业,在 AI 产品化方面仍处于初级阶段。阻碍 AI 算法概念验证 (PoC) 成为真正硬件部署的主要差距仍然存在。

5G 产业潜力巨大,但行业如何才能克服成本、功耗与性能等相关挑战,确保 5G 在第二次浪潮中大获成功?无线行业的未来取决于是否能够综合运用先进技术最大化系统性能,同时最优化成本与功耗以提供极具竞争力的产品。

I2C 总线的两根信号线 SCL 和 SDA 需要上拉才能正常工作,当板卡上没有合适的硬件设置或者没有合适的 I2Cslave 设备,我们就无法进行 I2C 软件测试。那么是否可以将两个 PSI2C 控制器通过 EMIO 接口互连起来呢?

Arm 发行的白皮书 "Cache Speculation Side-channels"用于发现 "Spectre" 辅助通道。 白皮书指出,DSB SYS 和 ISB 的组合可防止随后的猜测。但是,对于在 DSB SYS + ISB 之后执行页面转换的单次加载、存储或其他内存操作,可推测在 DSB SYS + ISB 完成之前的初始查找中是否发生了 TLB 错误,并填充新的 TLB 条目。

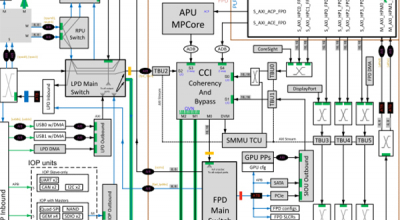

MPSoC的DDR控制器的数据通道上集成了 AXI performance monitors (APM)。具体情况,可以参考Xilinx UG1085 (v2.2)中Chapter 15的“Figure 15‐1: PS Interconnect”或者Figure 17-1。

有时我们需要为官方 IP 或者自己创建的 IP 生成 kernel module,然后在 linux kernel space 里使用 kernel module 来控制这个 IP。如果要使用 IP 中断,我们需要在 kernel module 代码里获取设备中断并建立中断服务程序。

每个 RPU 处理器都有 1 个 DBGDRAR 寄存器,其中包含 CoreSight 根 ROM 表的地址。但读取此寄存器时会返回错误的地址 0xfe800003。正确的返回地址应为 0xf0800003。尝试访问包含错误地址的 CoreSight 根 ROM 表将导致 RPU 处理器发生软件异常。

不久以前,从算法到现场机器学习( ML )模型仍然需要经历漫长而复杂的道路。对于一些企业而言,如果能够接触到具有神经网络部署经验的 ML 专家,则可能会有一些选择,但其开发工作却非常耗时。赛灵思依托 Vitis 统一软件平台以及近期推出的 KRIA SOM (System-on-Module),缩短了这一过程。