加速 AI 推断的三个关键因素

judy 在 周三, 10/28/2020 - 09:59 提交

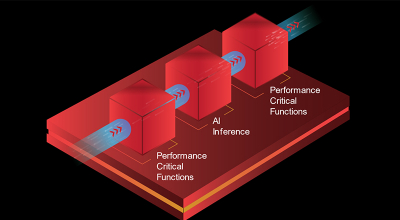

AI 已经开始改变我们生活的方方面面,推动了显著的社会进步。从自动驾驶汽车到 AI 辅助医疗诊断,我们正处于一个真正的变革时代的开端。但是,有机遇就会有挑战。AI 推断作为采用经训练的机器学习算法开展预测的过程,无论是部署在云端、边缘还是终端,都要求在严格的功耗预算下提供优异的处理性能。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

AI 已经开始改变我们生活的方方面面,推动了显著的社会进步。从自动驾驶汽车到 AI 辅助医疗诊断,我们正处于一个真正的变革时代的开端。但是,有机遇就会有挑战。AI 推断作为采用经训练的机器学习算法开展预测的过程,无论是部署在云端、边缘还是终端,都要求在严格的功耗预算下提供优异的处理性能。

这是《创建 Vitis 加速平台》系列的第 3 篇博文。在前文中,我们讲解了如何创建硬件和软件工程。在本文中,我们将讲解如何在 Vitis™ 中将所有这些工程封装在一起。

Vitis 2019. - 对 VCK190 进行编程时出现 PLM 停止错误的问题解答。

当使用 Dynamic Function eXchange(部分重新配置)流程时,该工具报告显示成功生成了比特流,没有 DRC 错误,但生成的部分比特流不正确。部分比特流下载后,时钟停止运行。

无论是设计测试和测量设备还是汽车激光雷达模拟前端(AFE),使用现代高速数据转换器的硬件设计人员都面临高频输入、输出、时钟速率和数字接口的严峻挑战。问题可能包括与您的现场可编程门阵列(FPGA)相连、确信您的首个设计通道将起作用或确定在构建系统之前如何对系统进行最佳建模。

本设计咨询涵盖了如下实现问题:时钟在驱动 UltraScale 或 UltraScale+ 架构的物理层块 (PHY) 时可能执行错误的反相操作。使用 Vivado 2020.1 或 Vivado 2020.1.1 时,PHY BITSLICE site 中包含的可选反相器 IPHY_OCLK_OPTINV 基于 INVERT 属性可能执行错误的反相操作。

本设计咨询涵盖了如下实现问题:时钟在驱动 UltraScale 或 UltraScale+ 架构的物理层块 (PHY) 时可能执行错误的反相操作。

使用 Vivado 2020.1 或 Vivado 2020.1.1 时,PHY BITSLICE site 中包含的可选反相器 IPHY_OCLK_OPTINV 基于 INVERT 属性可能执行错误的反相操作。

ZDMA应用例子xzdma_simple_example.c 缺省只运行一次。在XZDma_SimpleExample()里的XZDma_SelfTest( )之后,把运行部分放进一个循环体,可以多次运行。测试工具是Xilinx SDK 2018.2.

文本是人类最具智慧、最有影响力的创造之一。文本中所蕴含的丰富、精确的高级语义可以帮助我们理解周遭世界,并用于构建可部署在真实环境中的自主运行解决方案。因此,自然环境下的自动文本读取,也称为场景文本检测/识别或 Photo OCR,已成为计算机视觉领域中关注度和重要性日益提高的研究课题。

XAPP1305 提供一个带 PCS/PMA 内核的 SGMII 示例,称之为“PS EMIO SGMII”。它不使用 FPGA 外部的 PHY 设备。对于我的使用案例,我想使用具有 SGMII 接口的外部 PHY 来连接。Linux 只能通过在设备树中设置 phy-handle 的 MDIO 管理一个 PHY。这个系统中有两个 PHY。怎么管理这两个 PHY?