【开源方案】PYNQ-DPU框架下的人工智能医学图像方案

judy 在 周二, 10/20/2020 - 09:36 提交

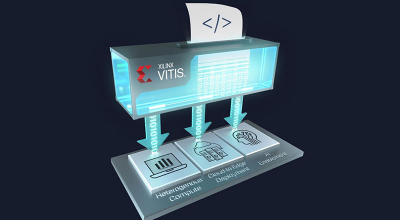

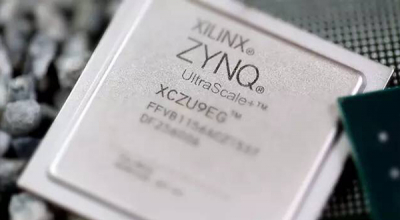

本方案基于Vitis-AI、ZCU104验证平台和AWS-IoT GreenGrass,其中Vitis-AI用于COVID-19深度学习模型的转换、量化和编译,将模型转换为DPU可运行的.elf文件;ZCU104验证平台完成基于X-Ray图像的COVID-19 CNN在线检测或用作AWS-IoT GreenGrass的边缘计算设备,完成COVID-19的边缘实时检测。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

本方案基于Vitis-AI、ZCU104验证平台和AWS-IoT GreenGrass,其中Vitis-AI用于COVID-19深度学习模型的转换、量化和编译,将模型转换为DPU可运行的.elf文件;ZCU104验证平台完成基于X-Ray图像的COVID-19 CNN在线检测或用作AWS-IoT GreenGrass的边缘计算设备,完成COVID-19的边缘实时检测。

有时我们需要在设计网表的基础上微调一下逻辑,这样可以无需修改代码,也无需重新做综合,在设计调试中可以节省时间同时维持其他逻辑无任何改动。这里带大家一起体验一下Vivado 的ECO流程,以vivado自带的Example Design为例, 直接用TCL命令修改网表,在正常的寄存器路径之间加一级LUT。

GCC编译代码时,缺省是在目录/usr/include查找头文件,在目录/usr/lib查找库文件。如果是交叉编译,就不能在主机的目录下查找头文件和库文件,因为它们包含的是主机的应用程序的文件。我们需要指定目标单板的头文件和库文件。对于这种需求,GCC使用选项sysroot来实现

Vivado Vitis 2020.1无法在Ubuntu部分版本上安装的解决办法

赛灵思可编程器件含有数百万个逻辑单元 (LC),并且集成的现代复杂电子系统也与日俱增。本高效设计方法指南提供了一整套最佳做法,旨在于较短的设计周期内完成此类复杂系统的创建。

有工程师反馈R5引导A53和R5的应用程序后,A53和R5的应用程序没有正确执行。因此做了一个MPSoC R5引导4个A53和两个R5的应用程序的例子。

这是《创建 Vitis 加速平台》系列的第 2 篇博文。在前文中,我们讲解了如何创建硬件以及如何通过 XSA 将元数据 (metadata) 传递给 Vitis™。在本文中,我们将讲解如何使用此 XSA 以及如何创建在目标平台上实现设计加速所需的软件镜像。

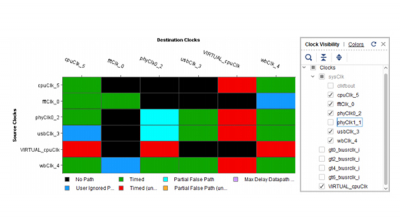

本手册详细介绍 Vivado工具的功能特色,包括 FPGA 设计的逻辑和时序分析以及工具生成的报告和消息。探讨达成时序收敛的方法,包括审查时钟树和时序约束、设计布局规划以及实现运行时间与设计结果的平衡。

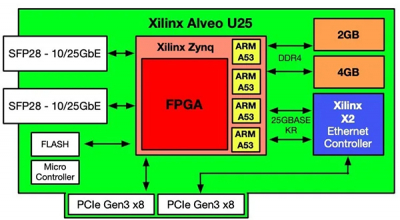

普通 NIC 定位于高效迁移服务器的网络数据包,通常包括不同程度的为优化性能而设计的传统卸载。SmartNIC 整合了多方面的附加计算资源,但是这些架构就像雪花一样各不相同,因此,我们将深入研究规模最大、最受欢迎的供应商所提供的几种方法。

Fractal(分形图形),是由IBM研究室的数学家曼德布洛特(Benoit.Mandelbrot,1924-2010)提出的,其维度并非整数的几何图形,而是在越来越细微的尺度上不断自我重复,是一项研究不规则性的科学。下面是一个最简单的例子,首先画一条线段,然后把它平分成三段,将中间那一段用一个等边三角形的两条边代替