创建 Vitis 加速平台第 1 部分:如何在 Vivado 中为加速平台创建硬件工程

judy 在 周三, 09/02/2020 - 15:22 提交

在本文中,我们将讲解如何在 Vivado® Design Suite 中完成平台准备工作,以便将其用作为 Vitis 中的加速平台。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

在本文中,我们将讲解如何在 Vivado® Design Suite 中完成平台准备工作,以便将其用作为 Vitis 中的加速平台。

描述

在《Virtex UltraScale+ FPGA 数据手册》(DS923) 中,XCVU27P-3E 器件和 XCVU29P-3E 器件的最低量产软件和速度规格已从 Vivado 工具 2019.2 v1.28 更新至 Vivado 工具 2020.1.1 v1.30。

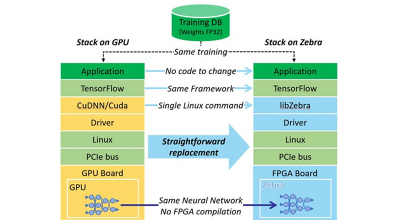

众所周知,实施一个完整的AI应用需要经历训练和推理两个过程。所谓“训练”,就是我们要将大量的数据代入到神经网络模型中运算并反复迭代,“教会”算法模型如何正确的工作

在《Zynq UltraScale+ MPSoC 数据手册》(DS925) 中,XAZU7EV-1Q 器件与 XAZU11EG-1Q 器件的最低量产软件和速度规格已从 Vivado 工具 2019.1.1 v1.26 更新至 Vivado 工具 2020.1.1 v1.30。

Versal 自适应计算加速平台 (ACAP) 是基于 TSMC 7nm FinFET 工艺技术构建的最新一代赛灵思器件。它利用高带宽片上网络 (NoC) 将代表处理器系统 (PS) 的标量引擎、代表可编程逻辑 (PL) 的自适应引擎与智能引擎有机结合在一起。本文将着重介绍智能引擎中所包含的 AI 引擎。

本期,小编为大家带来暑期学校优秀项目的图像处理合集。这些项目均利用了摄像头,获取图像后进行识别。

在我与客户交流时,常被问到这个问题。也许措辞并非完全如此,但大致是下面这样:“为什么我要升级到 Versal™ ACAP?现在是时候这样做了吗?”这是一个很好的问题,而且答案也很简单,那就是——“具体情况具体分析”。

在 5G 商业化方兴未艾之际,对于 5G 能给我们这个日益互联的世界带来哪些影响,人们充满憧憬。事实上,随着 5G 技术得到更广泛的部署,今后十年我们预计将看到消费者、企业和经济的面貌被 5G 功能重塑一新。

在 2019.1 版本中,在以下情况下,当数据小于 104 字节时,XilSecure 不支持 SHA3 散列计算:

输入数据处于非字对齐状态

输入数据来自非字对齐地址。