开发者分享 | 使用 Report QoR Assessment 命令

judy 在 周五, 07/24/2020 - 15:41 提交

Report QoR Assessment (RQA) 用于详述您的设计 QoR 目标实现的可能性。如果此命令返回的结果与您的期望不符,那么本篇博文包含了有关您可采取的后续行动的附加信息。本篇博文不仅适合首次使用这些命令的新用户,对于有经验的用户应该同样很实用。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

Report QoR Assessment (RQA) 用于详述您的设计 QoR 目标实现的可能性。如果此命令返回的结果与您的期望不符,那么本篇博文包含了有关您可采取的后续行动的附加信息。本篇博文不仅适合首次使用这些命令的新用户,对于有经验的用户应该同样很实用。

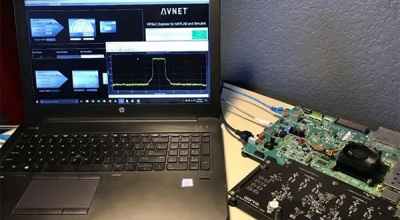

在某些情况下,比如远程工作时,可能需要访问本地不可得的器件。本篇简介教程演示了如何共享并访问位于远程实验室内的开发板或归同事所有的开发板。

AI芯片优化主要有三个方面:算法优化,编译器优化以及硬件优化。算法优化减少的是神经网络的算力,它确定了神经网络部署实现效率的上限。编译器优化和硬件优化在确定了算力的基础上,尽量最大化硬件的计算和带宽性能。经历了一年多的理论学习,开始第一次神经网络算法优化的尝试。之所以从一个FPGA开发者转向算法的学习,有几个原因

ORB特征是一种图像识别、追踪和匹配中常用的特征,大名鼎鼎的ORB-SLAM就是使用的这一特征。它提取FAST特征点,并通过特征点附近的窗口矩计算特征点的方向,含方向的FAST特征也被称为oFAST特征。对提取到的oFAST特征,进一步计算BRIEF描述子。ORB特征包含了两部分,一是特征点位置,二是它的BRIEF 256位描述子

一些 5G 系统的制造商正在转向更高水平的硬件集成,并在片上系统(SoC)设备中整合射频转换器和基带处理引擎,以解决功耗和电路板空间问题。虽然这种集成有好处,但负责这些系统表征的工程师面临着访问数据的新挑战,因为之前的独立射频数据转换器现在将与 FPGA 和处理器在同一芯片上进行组合

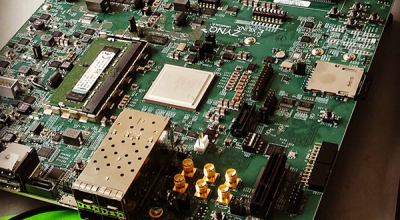

现代 RF 信号链对于跨多通道的数据转换器性能具有极高的要求。换言之,对于赛灵思 RF Data Converter 而言,关键要求之一是在多个 ADC/DAC Tile、RFSoC 器件甚至开发板之间都必须保持同步。了解赛灵思如何探索多块同步 (Multi-Tile Synchronization) 问题解决之道

近期,在推动 IT 基础设施向异构计算转型的过程中,赛灵思与 VMware 展开协作,在 VMware 的云计算虚拟化平台vSphere上测试 FPGA 加速。由于赛灵思 FPGA 越来越广泛地应用于 ML 推断加速,本文将展示的是如何将赛灵思 FPGA 与 VMware vSphere 相结合,在虚拟部署和裸机部署上实现基本相同的高吞吐量、低时延 ML 推断性能。

在OpenAMP的应用程序中,经常看到地址被设置成RPMSG_ADDR_ANY。在通信过程中,为什么可以把源地址、目的地址设置成任意值?这个宏的名字不够清楚,它的本意是让系统自动选择。如果设置源地址为RPMSG_ADDR_ANY,则系统自动选择一个空闲的源地址。

不同使用场景,对芯片的性能和功耗要求不一样。为了测试Xilinx MPSoC PS侧的最低功耗,基于ZCU106单板做了功耗优化。为了方便,使用最简单的软硬件环境。软件使用死循环做串口打印,硬件保留了如下模块。

EasyDL是百度大脑推出的定制化AI训练及服务平台,支持面向各行各业有定制AI需求的企业用户及开发者使用。支持从数据管理与数据标注、模型训练、模型部署一站式AI开发流程,通过原始图片、文本、音频、视频类数据经过EasyDL加工、学习、部署可发布为公有云API、设备端SDK、本地化部署及软硬一体产品