【分享】Xilinx最新7nm器件Versal处理器列表,及Vitis能创建的模板软件工程

judy 在 周一, 06/01/2020 - 11:20 提交

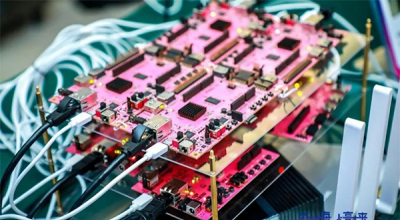

Xilinx的28nm、16nm SoC在业界应用非常广泛。最近也发布了7nm的SoC器件Versal VC1902和对应的开发板VCK190。Versal是新一代的异构计算平台,包含A72、R5、及内部管理用的CPU。Versal的软件开发工具是Vitis。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

Xilinx的28nm、16nm SoC在业界应用非常广泛。最近也发布了7nm的SoC器件Versal VC1902和对应的开发板VCK190。Versal是新一代的异构计算平台,包含A72、R5、及内部管理用的CPU。Versal的软件开发工具是Vitis。

时延敏感网络(TSN, Time Sensitive Network)是指能保证时延敏感流的服务质量,实现低时延、低抖动和零丢包率的网络。时延敏感流可分为周期时延敏感流(PTS, Periodic Time Sensitive),比如工厂里的循环控制指令、同步信息,和非周期/零星时延敏感流(STS,Sporadic Time Sensitive),比如事件告警信息。

本篇博文旨在演示其构建方式及其用于实践 IP 的机制。我觉得这部分内容值得讲一讲,因为只要您能够充分理解测试激励文件,就可以将其作为有效的模板来用于将 RF Data Converter IP 构建到自己的仿真设置中。

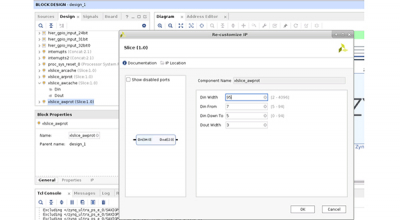

MPSoC 为PL提供了96个GPIO,通过EMIO管脚链接到PL。普通PL设计,一般只会用到几个GPIO管脚。可以使用Vivado IPI中的Slice IP, 从其中分出指定数量的管脚。

说在前面,本文分享了两个视频,从 DFX 的布局规划,再到布局规划的进阶。两个视频,20分钟帮您快速掌握 DFX 的布局规划...

随着赛灵思 Alveo 自适应计算加速卡的发布,数据中心各种工作负载开启了自适应计算加速的历程。本期小编特整理了有关 Alveo 的一批中文文档,以供各位随时下载和查阅。

数字信号对载波信号的振幅调制称为振幅键控,即ASK。在2ASK调制系统中,数字信息只有0和1两种,所调制的载波信号的幅度变化状态也只有两种:无载波输出时代表发送0;有载波输出时代表发送1。在4ASK调制系统中,数字信息就有00、01、10、11四种,需要载波信号幅度的4个电平状态表示

随着高带宽内存(HBM)的发展,FPGA正变得越来越强大,HBM 给了FPGA 更多能力去缓解再一些应用中遇到的内存带宽瓶颈和处理更多样的应用。然而,HBM 的性能表现我们了解地还不是特别精准,尤其是在 FPGA 平台上。这篇文章我们将会在HBM 的说明书和它的实际表现之间建立起桥梁

Xilinx的开发板ZCU102支持休眠到内存(suspend-to-ram)。休眠到内存时,DDR进入自刷新,MPSoC被关电,完全不耗电。唤醒时,MPSoC根据外部输入信号判断出不是上电启动而是休眠,就从DDR读出系统状态,恢复系统

本案例来源于第三届全国大学生FPGA创新设计竞赛中江南大学的OpenHEC lab团队,他们的作品基于PYNQ开源软件框架。PYNQ框架提供了完整的访问FPGA资源的Python library,通过高层次的封装,让开发者通过Python API就可以轻松调用FPGA内的模块或算法,加速产品开发部署