Xilinx大神都懂的数字运算单元—DSP48E1

judy 在 周六, 05/09/2020 - 09:26 提交

FPGA中DSP资源是宝贵的且有限,我们在计算大位宽的指数、复数乘法、累加、累乘等运算时都会用到DSP资源,如果我们不了解底层的DSP特性,很多设计可能都无法进行。逻辑综合往往是不可控的,为了能够充分利用DSP资源,我们需要对DSP48E1有所了解

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

FPGA中DSP资源是宝贵的且有限,我们在计算大位宽的指数、复数乘法、累加、累乘等运算时都会用到DSP资源,如果我们不了解底层的DSP特性,很多设计可能都无法进行。逻辑综合往往是不可控的,为了能够充分利用DSP资源,我们需要对DSP48E1有所了解

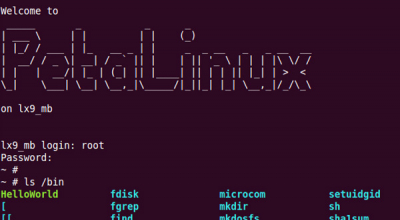

PetaLinux以前的版本中,在project-spec/meta-user/conf/petalinuxbsp.conf里添加MALI_BACKEND_DEFAULT = "wayland"”,在编译时选择图形backend。在PetaLinux 2019.1里,默认集成多个图形backend。运行时,可以根据需要选择图形后端。这样更方便调试。

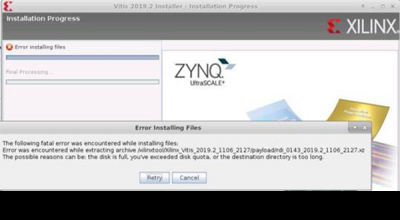

解决Ubuntu 16.04安装Vitis 2019.2失败的问题

心跳包就是在客户端和服务器间定时通知对方自己状态的一个自己定义的命令字,按照一定的时间间隔发送,类似于心跳,所以叫做心跳包。心跳包在GPRS通信和CDMA通信的应用方面使用非常广泛。数据网关会定时清理没有数据的路由,心跳包通常设定在30-40秒之间

本答复记录涵盖在 HyperLynx 中创建 IBIS-AMI 仿真测试平台的步骤。以 UltraScale+ GTY IBIS-AMI 模型为例。本教程使用 HyperLynx VX.2.4。

机器视觉系统中,镜头相当于人的眼睛,其主要作用是将目标的光学图像聚焦在图像传感器(相机)的光敏面阵上。视觉系统处理的所有图像信息均通过镜头得到,镜头的质量直接影响到视觉系统的整体性能。下面对机器视觉工业镜头的相关专业术语做以详解。

Xilinx提供了完整的V4L2的驱动程序,Xilinx V4L2 driver。处于最顶层的驱动程序是V4L2框架的视频管道(Video pipeline)驱动程序,也叫桥驱动程序(bridge driver),主要代码在文件xilinx-vipp.c中。在V4L2框架中,整个视频管道(Video pipeline)可以通过媒体设备(/dev/media)配置

对于FPGA开发而言,仿真是开发流程中必不可少的一步,也是非常重要的一步,仿真是将RTL代码模拟运行,得到module中信号波形,再进行功能分析的过程。强大的功能与速度兼具的modelsim仿真就是你开发过程的最合适的选择了,下面我以简单的24进制计数器带各位熟悉modelsim仿真流程及波形

现场可编程门阵列 (FPGA) 具有诸多特性,无论是单独使用,抑或采用多样化架构,皆可作为宝贵的计算资产;但是许多设计人员并不熟悉 FPGA,亦不清楚如何将这类器件整合到设计中。解决办法之一是深入研究主要供应商提供的 FPGA 架构及相关工具;本文则从 Xilinx 产品系列开始着手

有两种方法可以将 Alveo 数据中心加速卡上 Quad SPI 部件的内容还原为出厂映像。 本答复提供一般性说明,以及带逐步说明的文档的参考。