位交织

judy 在 周二, 03/10/2020 - 14:53 提交

当调制方式为16-AQM,64-QAM和256-QAM时需要做位交织,交织的目的是将突发的错误分散开来,把一个较长的突发差错离散成随机差错,再用随机差错的编码(FEC)等信道编码技术消除随机差错,提高通信的可靠性。交织的越深,抗突发错误的能力也越强

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

当调制方式为16-AQM,64-QAM和256-QAM时需要做位交织,交织的目的是将突发的错误分散开来,把一个较长的突发差错离散成随机差错,再用随机差错的编码(FEC)等信道编码技术消除随机差错,提高通信的可靠性。交织的越深,抗突发错误的能力也越强

学艺不精的后果就在于:学而不思则罔。圣人太厉害了,总结得很到位。比如最近项目中涉及到浮点和定点的转换,自己就有点蒙,边看边实验,还算理解了,作文以记之

最近有朋友问,公众号为什么起名叫网络交换FPGA?今天这篇文章就来回答一下。我们将从网络交换的历史讲起,也正如机器学习也赶上了ASIC工艺发展才引起革命性的变化一样。技术发展的历程中,总有那些看似不相关的技术结合起来,结果导致翻天覆地的变化

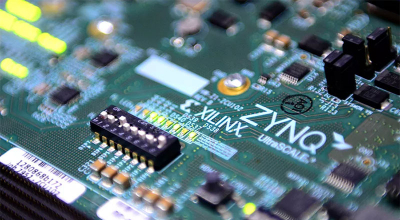

近来,几乎每个赛灵思 IP 都使用 AXI 接口。Zynq®、Zynq MP、MicroBlaze™ 和全新的 Versal™ 处理器都无一例外使用 AXI 接口。因此,AXI 接口已成为几乎所有新的赛灵思器件设计中不可或缺的一部分。充分了解其基础知识对于赛灵思器件的设计和调试都很有帮助。本篇博文将介绍赛灵思器件上的 AXI3/AXI4 的相关基础知识。

Xilinx Floating-Point IP

对数字信号的比特进行随机处理,减少连0和连1的出现,从而减少码间干扰和抖动,方便接收端的时钟提取;同时又扩展了基带信号频谱,起到加密的效果。为了保证在任何情况下进入传输信道的数据码流中“0”与“1”的概率都能基本相等,传输系统会用一个伪随机序列对输入的传送码流进行扰乱处理,将二进制数字信息做“随机化”处理

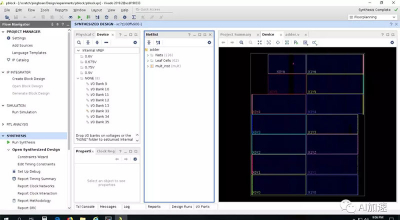

Pblock是对一些逻辑实行物理上的约束,即把一些逻辑绑定到FPGA上固定的资源区域内。它是优化走线,改善时序的一种很重要方法。Pblock的大小限定了该逻辑单元使用的FPGA资源,pblock的位置限定了逻辑单元在FPGA中的位置。通常一个pblock大小不要超过总设计资源的20%。如果pblock占比资源很大,就要将一个pblock划分给更底层的逻辑

本文深维科技联合创始人兼CEO樊平详细剖析了图片加速的必要性、当前实际的图片解决方案与部署方式以及如何通过FPGA+CPU异构计算的方案维护用户体验与服务成本新平衡。

做深度学习加速器已经两年了,从RTL设计到仿真验证,以及相应的去了解了Linux驱动,深度学习压缩方法等等。今天来捋一捋AI加速器都涉及到哪些领域,需要哪些方面的知识。可以用于AI加速器的主要有三种不同架构的器件种类:CPU,GPU,AI芯片/FPGA。

关键内容提要:

(1) FPGA IO命名方式;

(2) FPGA的上电时序

今天想和大家一起聊聊FPGA的IO。