Xlinx IP Core实现FFT变换——为什么你的matlab数据无法严格比对?

judy 在 周二, 03/03/2020 - 10:33 提交

Xilinx FFT IP介绍:缩放因子等参数应该注意的matlab数据比对细节。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

Xilinx FFT IP介绍:缩放因子等参数应该注意的matlab数据比对细节。

从 2019.2 版开始,赛灵思 SDK 开发环境已统一整合到全功能一体化的 Vitis™ 统一软件平台中。尊敬的 SDK 用户,您只需轻点几下鼠标即可体验这一功能丰富的工具!

由于XDC约束是按顺序应用的,并且基于明确的优先级规则进行优先级排序,因此必须仔细检查约束的顺序。如果多个物理约束发生冲突,则最新约束将获胜。 例如,如果通过多个XDC文件为I / O端口分配了不同的位置(LOC),则分配给该端口的最新位置优先。

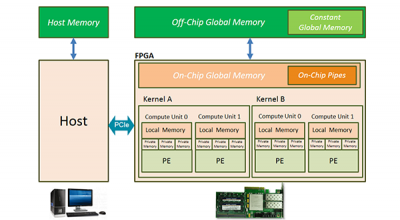

在OpenCL中提供的存储模型中,有如下几种Memory类型。Host Memory:Host Memory指的是连接在主板上的内存条,仅供host进行数据读取。Off-Chip Global memory:Off-Chip Global memory 指的是在FPGA板卡上通过硬件与FPGA芯片连接的内存条。数据存取所花费的时间相对较长,但是容量相对较大。

Zynq的开发四种方式:纯PL开发,纯PS开发(helloworld),PS+PL(无操作系统,跑裸跑程序),PS+PL(跑操作系统)。

什么是XPM?可能很多人没听过也没用过,它的全称是Xilinx Parameterized Macros,也就是Xilinx的参数化的宏,跟原语的例化和使用方式一样。可以在Vivado中的Tools->Language Templates中查看都有哪些XPM可以例化。

搜索float双击Floating-point。Operation Selection 我们这里选择浮点数的加减法验证。Precision of Inputs 我们选择单晶浮点数(Single),指数位宽Exponent Width 8bit 尾数位宽24 bit

FPGA中乘法器是很稀缺的资源,但也是我们做算法必不可少的资源。7系列及之前的FPGA都是25x18的DSP,UltraScale中是27x18,我们可以通过调IP Core的方式或者原语的方式来进行乘法操作。在里面可以设置有符号还是无符号数乘法。

Xilinx Floating-Point IP主要分为操作数s_axis_a,s_axis_b,s_axis_c,可编程操作s_axis_operation和输出结果m_axis_result。

Vivado相比与上一代开发工具ISE,一个巨大的提升就是全面支持Tcl脚本语言。由于全面支持Tcl脚本,所以可以利用Tcl来做一些好玩的事情。这里抛砖引玉,分享一点关于Vivado Tcl的使用小心得。