【分享】快速实现Flash自动烧写功能

judy 在 周二, 04/21/2020 - 09:55 提交

Xilinx SDK Flash Programmer 支持Flash烧写。但是市场上Flash型号众多。不是所有的Flash型号,Xilinx SDK Flash Programmer都支持。如果遇到不支持的Flash型号,可以自己通过U-Boot实现一个简易的Flash Programmer。本文以Xilinx SDK 2018.3为例。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

Xilinx SDK Flash Programmer 支持Flash烧写。但是市场上Flash型号众多。不是所有的Flash型号,Xilinx SDK Flash Programmer都支持。如果遇到不支持的Flash型号,可以自己通过U-Boot实现一个简易的Flash Programmer。本文以Xilinx SDK 2018.3为例。

在Xinlinx的ZYNQ中,拥有ARM+FPGA这种架构,每款产品均带有双精度浮点的双核ARMCortex-A9MPCore处理系统,ARM(PS端)具有比较强的事务管理功能,可以用来跑界面以及应用程序等,其优势主要体现在控制方面,里面整合了很多现成的硬件资源供编程调用。FPGA(PL端)灵活性强,拥有更大的并行度和计算能力

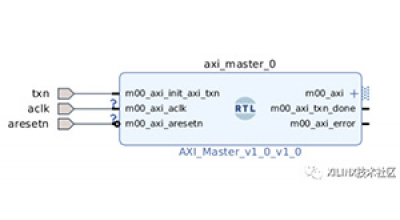

在某些情况下,通过嗅探 AXI 接口来分析其中正在发生的传输事务是很有用的。在本文中,我将为大家演示如何创建基本 AXI4-Lite Sniffer IP 以对特定地址上正在发生的读写传输事务进行计数。首先,编写 HDL (Verilog) 代码,然后将其封装为 IP,最后将此 IP 添加到 IP IntegratorBlock Design (BD) 中。

Xilinx文件基本都放在国外的服务器上。如果直接使用浏览器下载,在国内下载,速度一般比较慢。如果超过时间没有下载完,连接还会失效,导致反复下载也不能成功,成功率比较低。为了提升Xilinx文件下载速度和可靠性的办法,建议使用专门的下载工具

CLB是指可编程逻辑功能块(Configurable Logic Blocks),顾名思义就是可编程的数字逻辑电路。CLB是FPGA内的三个基本逻辑单元。CLB的实际数量和特性会依器件的不同而不同,但是每个CLB都可配置,在Xilinx公司的FPGA器件中,CLB由2个 相同的SliceL或则一个SliceL和一个SliceM构成

近来卷积神经网络(CNN)的研究十分热门。CNN发展的一个瓶颈就是它需要非常庞大的运算量,在实时性上有一定问题。而FPGA具有灵活、可配置和适合高并行度计算的优点,十分适合部署CNN。

在 AXI 基础第 2 讲 一文中,曾提到赛灵思 Verification IP (AXI VIP) 可用作为 AXI 协议检查工具。在本次第4讲中,我们将来了解下如何使用它在 AXI4 (Full) 主接口中执行验证(和查找错误)

神经网络加速器基本上是一个中介拓扑架构的神经网络加速器,其通过指令解析模块将不同指令分发到不同的数据处理模块。这些数据处理模块共享片上的存储。这种结构的优点有:

傅立叶变换是数字信号处理领域一种很重要的算法,可以将一个信号从时域变换到频域。傅立叶原理表明:任何连续测量的时序或信号,都可以表示为不同频率的正弦波信号的无限叠加。根据原信号的不同类型,傅里叶变换可以分为四种类别

在这篇新博文中,我们来聊一聊如何将 AXI VIP 添加到 Vivado 工程中,并对 AXI4-Lite 接口进行仿真。随后,我们将在仿真波形窗口中讲解用于AXI4-Lite 传输事务的信号。