Xilinx 视频实时转码一体机解密系列一:两大一体机开启低成本高品质视频直播新时代

judy 在 周三, 06/24/2020 - 09:27 提交

近日,赛灵思发布重磅消息,同时推出两款易于扩展的、超高密度视频转码专用视频实时转码一体机。自本期开始,我们将通过一系列解密文章,为您揭开这一与众不同的实时转码一体机...

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

近日,赛灵思发布重磅消息,同时推出两款易于扩展的、超高密度视频转码专用视频实时转码一体机。自本期开始,我们将通过一系列解密文章,为您揭开这一与众不同的实时转码一体机...

PYNQ-PRIO是一个介绍如何利用FPGA部分可重配置特性和PYNQ框架提供的方便的API,对FPGA分时复用,提高FPGA灵活性的项目。可重配置是指在一个FPGA工程中,划分了静态逻辑部分和动态逻辑部分,静态逻辑部分是指在运行过程中逻辑不变的部分

一个工程师打算在命令行里编译Xilinx SDK工程,以便集成进入其它自动化构建工具。Xilinx SDK工程都支持在命令行编译。在命令行里编译Xilinx SDK工程前,需要执行call C:/Xilinx/SDK/2019.1/settings64.bat,设置编译环境。

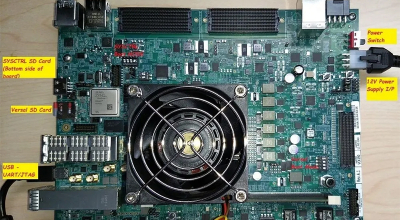

Versal™ ACAP(自适应计算加速平台)是高度集成化的多核计算平台,可通过灵活的自适应能力来满足不断变化的动态算法的需求。VCK190 是赛灵思最早发布的 Versal AI Core 评估器件之一。本篇博文将为您详解如下所述设计创建步骤:

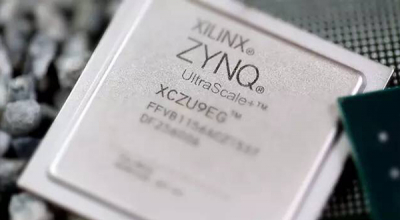

本文介绍MPSoC的芯片启动流程

结合 SDSoC 和赛灵思 SDK,SDAccel 流现在是 2019.2 Vitis™ 统一软件平台的组成部分,便于开发者针对赛灵思器件上的所有软件任务使用统一平台。下面分享来自 DesignLinx 公司高级嵌入式软件工程师 Nathan Sullivan 所撰写的技巧

本文展示了通过使用 Design Gateway 的 NVMeG3-IP 内核在 Xilinx 的 ZCU102 评估套件上实现 NVMe 固态硬盘 (SSD) 接口的解决方案,该方案可实现惊人的快速性能:写入速度达 2,319 MB/s,读取速度达 3,347 MB/s。

本文简要介绍了 ToF 传感器的工作方式。然后,本文将介绍 Digilent 的 Pmod ToF 板,并说明如何将其与 Digilent 的 Zybo Z7-20 开发板结合使用,以评估 ToF 技术并在自己的设计中快速部署光学距离感测。

MPSoC EV 系列支持H.265编解码。在规格中,1080p编解码都可以达到8路1080p30,总体相当于1080p240。使用2018.3 VCU TRD 实际测试,性能更好。

数字频率调制是利用载波的频率传输信息的一种调制方式,FSK是在ASK之后出现的一种调制方式,抗衰落能力较强,在一些衰落信道中应用广泛。