【开发者分享】解决方法论问题可提升实现的一致性

judy 在 周五, 06/12/2020 - 09:49 提交

改进设计时,如果 QoR 不升反降,那么您势必将面临如下选择。是继续修复?还是重新寻找新的解决方案?您可能忽视了某些问题,或者可能工具在运行给定轮次时性能有所下降。能否快速准确解答这一问题恰恰是判断 FPGA 工程师是否足够出色的标准之一。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

改进设计时,如果 QoR 不升反降,那么您势必将面临如下选择。是继续修复?还是重新寻找新的解决方案?您可能忽视了某些问题,或者可能工具在运行给定轮次时性能有所下降。能否快速准确解答这一问题恰恰是判断 FPGA 工程师是否足够出色的标准之一。

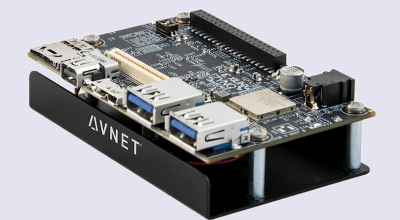

Ultra 96™ 是构建边缘用例机器学习应用的绝佳平台。Zynq® MPSoC ZU3 器件采用的 96 电路板的外形尺寸以及可编程逻辑,使其能够灵活地添加用于此类终端应用视频输入的通用 MIPI CSI2 RX 标准接口。同时为了驱动高性能、低功耗机器学习边缘应用,也可以将赛灵思深度学习处理单元 ( DPU ) 集成到设计中。

PetaLinux是Xilinx基于Yocto推出的Linux开发工具。Yocto是业界主流的Linux发行版的构建工具,它不仅可以从源代码编译Linux 内核,还可以编译Linux发行版必须的数以千计的的应用程序,功能非常强大。Yocto的出现,大幅度降低了构建嵌入式Linux发行版的难度

有些应用中,需要降低Xilinx MPSoC的功耗。缺省设置中,R5/GPU都被使能。如果需要省电,可以在Vivado里关闭R5/GPU。步骤如下:

1. 选中 MPSoC IP,在右键菜单中选择Block Properties.

2. 在窗口Block Properties中,选择Properties.

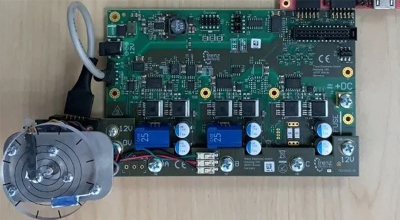

IIoT-SPYN是一个基于IIoT-EDDP开源平台和PYNQ软件框架的项目,它展示了如何在PYNQ开源框架下对电机进行控制、监视、捕获数据、可视化和分析。PL侧包含了对电机控制、状态采集的模块。在PYNQ中加载比特流后,就可以访问到这些已实现好的模块,对电机进行控制和状态检测。

振幅键控信号的解调主要有包络检波和同步检测两种方法,后者又被称为相干解调。相干解调需要提供与输入同频同相的载波信号,通常需要采用锁相环技术实现载波信号的提取,较为复杂,这里采用非相干解调的方法实现ASK解调,只需要将输入信号经过整流滤波即可得到基带信号。

XAPP1247 是对应使用屏障镜像时的多重启动 (Multiboot) 和回退 (Fallback) 的示例应用。本篇博文提供了一种屏障定时器流程测试方法以及使用此方法时可能出现问题。

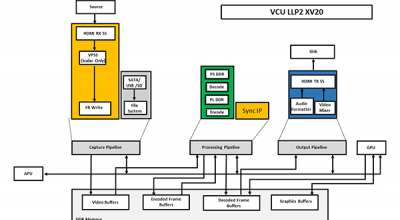

运行 Xilinx Low Latency PL DDR XV20 HDMI Video Capture and Display,可以测试HDMI输入输出,和VCU的低延时编码。Xilinx wiki的文章MPSoC VCU TRD 2019.2 - Xilinx Low Latency PL DDR XV20 HDMI Video Capture and Display以H.264和4K分辨率为例。

下面记录H.265和1080p分辨率的运行命令。

得益于人工智能的发展,它在机器人、物联网和智能个人助理(如Siri和Alexa)等方面创造了惊人的发展。那什么是人工智能呢?人工智能最简单的定义是:收集有关世界的数据,并利用这些数据进行短期和长期的预测。

Linux下,可以在设备树里保留一段内存,留给用户自己管理和使用,Linux保证不会使用保留内存。在使用中,有人发现,保留内存不能使用非对齐的方式访问。经研究,如果在保留内存时,声明了“no-map”属性,Linux会把这段内存映射为strongly order模式,不支持非对齐的方式访问。