【干货分享】升级Zynq-7000 XIP 参考设计到Xilinx SDK 2018.3

judy 在 周二, 04/28/2020 - 14:52 提交

有些应用中,单板没有DDR,OCM又不够存储所有数据和指令。这种情况下,Xilinx提供了参考设计Zynq-7000 AP SoC Boot - Booting and Running Without External Memory,把代码和只读数据放在QSPI Flash中运行程序,这就是execute in place (XIP)。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

有些应用中,单板没有DDR,OCM又不够存储所有数据和指令。这种情况下,Xilinx提供了参考设计Zynq-7000 AP SoC Boot - Booting and Running Without External Memory,把代码和只读数据放在QSPI Flash中运行程序,这就是execute in place (XIP)。

数字下变频是一种广泛应用于数字无线电接收机的数字信号处理技术,其主要目的是经过数字混频将A/D转换输出的中频信号搬移至基带,然后通过滤波,抽取完成信道提取的任务,主要的电路模块由四部分组成:数控震荡、数字混频、数字滤波、采样抽取。

终于到了今天的猪脚-SerDes,为什么拿SGMII和SerDes进行对比,主要原因是,SerDes是一个串行接口,和SGMII很像,和GMII几乎没有什么交集,所以两者对比就没有什么实际意义,所以只进行SGMII和SerDes进行对比。

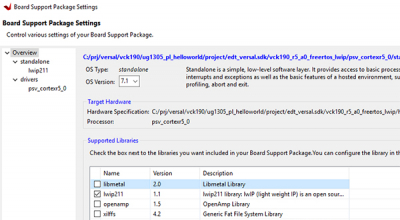

Xilinx的SoC在业界应用非常广泛。对应的开发工具SDK也很成熟。在SDK里,每一个baremetal工程,对应一个BSP工程,它包含一些Xilinx提供的公共模块,比如硬件的驱动、freertos、LWIP等。在BSP工程的右键菜单中,选择BSP setting,可以配置BSP工程包含的的公共模块。

某些应用程序小,可以全部放在Zynq-7000的256KB OCM上运行。这时,修改FSBL,可以把APP和FSBL编译成一个可执行文件,FSBL初始化硬件后,就直接运行应用程序。这种情况下,单板没有DDR。

本设计咨询主要面向 7 系列和 Virtex-6 FPGA,其中包含赛灵思针对 2020 年 4 月 15 日发布的一篇有关破解比特流加密的文章的回应,详情将于“USENIX Security 2020”大会上发表

图像处理算法在各种场景中都有广泛应用,借助于FPGA并行计算的优势可以将算法性能有效提升,但为了提升系统整体性能,仅仅提升某一部分的性能是不够的,一个好的方法是在FPGA内实现全部视频输入输出接口和图像算法的完整通路

PetaLinux环境下,也可以使用Yocto/openembedded的bitbake。Xilinx ug1144有详细说明。为了方便,我编写了以下脚本,导入bitbake需要的环境。将下列脚本保存为sh文件,使用source导入,之后就能使用bitbake。脚本的第一个输入参数是PetaLinux版本号,比如2019.2。

在本文中,您将了解有关内部集成电路总线(I2C 或 IIC)的基础知识以及将此协议总线应用于短距离通信的方法。I2C 属于串行通信协议,供双线接口用于连接 EEPROM、传感器、RTC、ADC/DAC 等低速器件以及嵌入式系统中的其它兼容 I/O 接口。

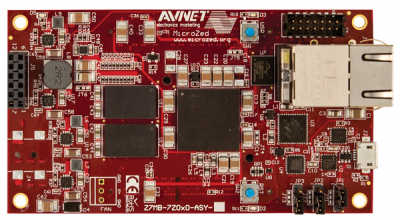

Vitis是Xilinx新推出的统一软件平台,可实现在 Xilinx 所有芯片(包括 FPGA、SoC 和 Versal ACAP)上开发嵌入式软件和加速应用。Xilinx主要宣传Vitis可以为异构平台的应用实现加速。其实,Vitis也能完美的支持嵌入式软件开发。下面以MicroZed单板为例,介绍在Vitis里如何创建嵌入式软件工程,并且编译和调试,直到启动。