vivado xilinx IOB = true的使用

demi 在 周四, 01/09/2020 - 13:12 提交

xilinx FPGA的资源一般指IOB,CLB,BRAM,DCM,DSP五种资源。其中IOB就是input/output block,完成不同电气特性下对输入输出信号的的驱动和匹配要求。

xilinx FPGA的资源一般指IOB,CLB,BRAM,DCM,DSP五种资源。其中IOB就是input/output block,完成不同电气特性下对输入输出信号的的驱动和匹配要求。

准则1:合适的代码风格

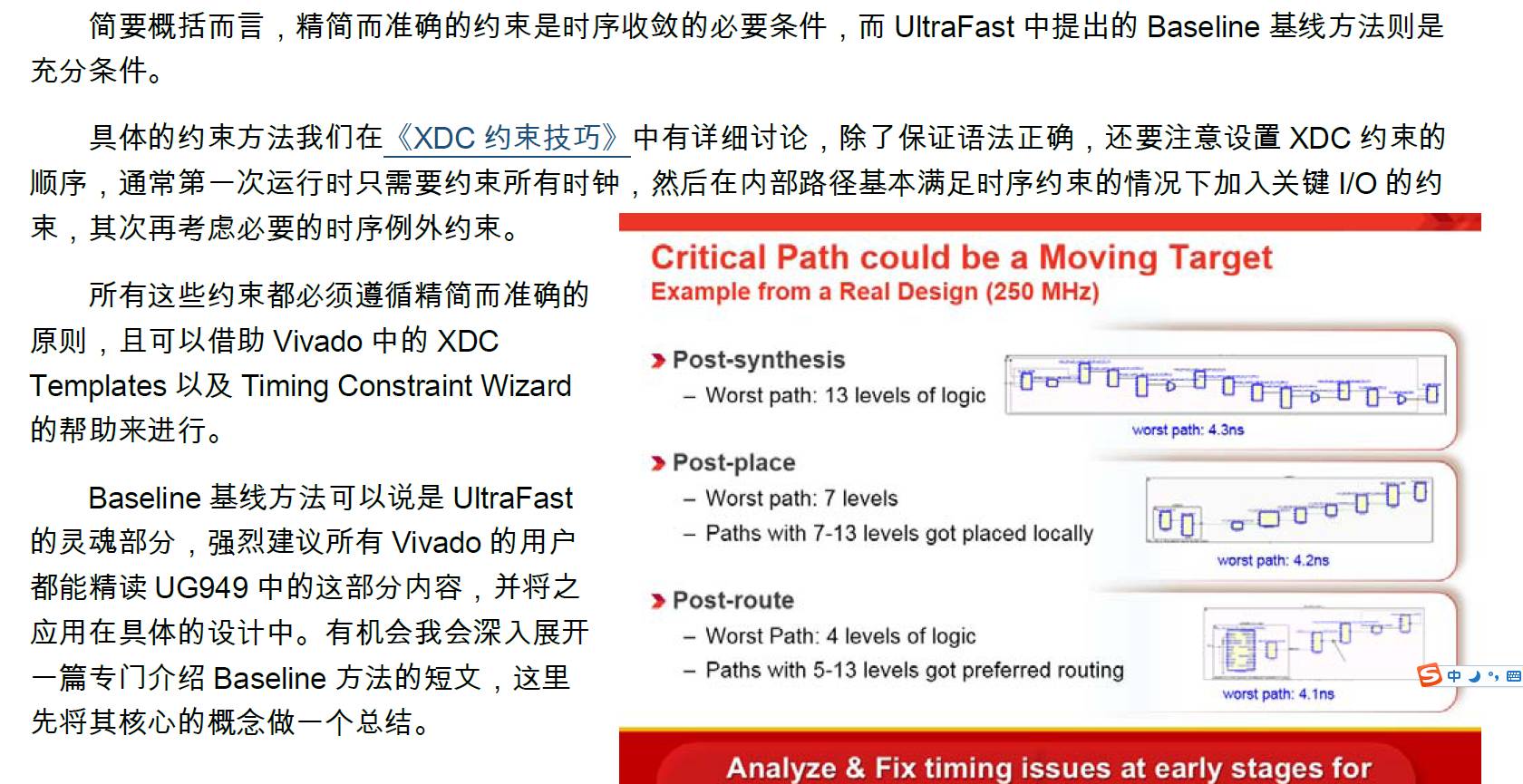

准则2:精准的时序约束

准则3:管理高扇出网络

准则4:层次化设计结构

在 Vivado/ISE 中遇到许可问题时,该怎么办呢?本文介绍了使用不同类型的许可证时可能遇到的不同问题。

许多 FPGA 设计都难以达成所期望的性能目标。原因不尽相同,以下列出的只是其中部分可能的原因:未遵循 UltraFast 设计方法;时序约束不良;过高资源利用率;控制集过多;未采用最优化时钟设置;逻辑层次过多,难以达成目标性能;布局规划不良;布线拥塞;因约束导致工具优化受限。

Vivado是Xilinx最新的FPGA设计工具,支持7系列以后的FPGA及Zynq 7000的开发。与之前的ISE设计套件相比,Vivado可以说是全新设计的。无论从界面、设置、算法,还是从对使用者思路的要求,都是全新的;在运行速度、算法优化和功能整合等很多方面都有了显著地改进。

有多种类型的时序违例可归类为脉冲宽度违例:最大偏差违例;最小周期违例;最大周期违例;低脉冲宽度违例;高脉冲宽度违例。

有多种类型的时序违例可归类为脉冲宽度违例:最大偏差违例;最小周期违例;最大周期违例;低脉冲宽度违例;高脉冲宽度违例。

XDC 是 Xilinx Design Constraints 的简写,但其基础语法来源于业界统一的约束规范SDC。XDC 在本质上就是 Tcl 语言,但其仅支持基本的 Tcl 语法如变量、列表和运算符等等,对其它复杂的循环以及文件 I/O 等语法可以通过在 Vivado 中 source 一个 Tcl 文件的方式来补充。

在 SystemVerilog 中,联合只是信号,可通过不同名称和纵横比来加以引用。其工作方式为通过 typedef 来声明联合,并提供不同标识符用于引用此联合。 这些标识符称为“字段”。

许多视频 IP 核都附带有示例设计。这些设计用于 IP 演示,并提供示例以供您在自己的设计中使用 IP 核时作为参考。赛灵思 HDMI IP 核分为两种:源端 (Source) IP 核 (HDMI 1.4/2.0 TX Subsystem) 和 Sink IP 核 (HDMI 1.4/2.0 RX Subsystem)。