使用 Vitis Model Composer 生成 FPGA IP 核

judy 在 周一, 04/14/2025 - 15:02 提交

今天的教程提供了创建自定义 IP 的分步指南,从算法开发到准备 IP 生成的模型,包括资源和时序分析,最后将其添加到 Vivado IP 目录。

今天的教程提供了创建自定义 IP 的分步指南,从算法开发到准备 IP 生成的模型,包括资源和时序分析,最后将其添加到 Vivado IP 目录。

未来汽车领域的发展愿景令人憧憬,其背后的驱动技术也因此备受关注。如今,传感器对于下一代汽车视觉与安全的发展至关重要

首个HiPi (High Performance Chips Interconnection Alliance) 标准的IP/VIP整体解决方案拥有优秀的商用级高带宽、低延迟、低功耗、协议完备等特性

本文介绍了一种集成了莱迪思FIR和iFFT IP核的新型OFDM调制器设计,简化了无线链路验证,降低了成本,缩短了开发时间。

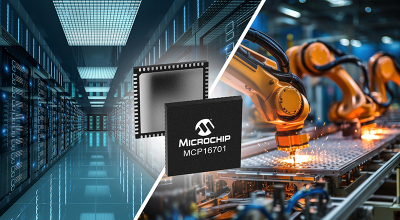

MCP16701 集成了八个可并联的 1.5A 降压转换器、四个 300 mA 内部低压差稳压器(LDO)和一个用于驱动外部MOSFET的控制器

MES2L676-100HP开发板(盘古100Pro+开发板)采用紫光同创logos2系列FPGA,芯片型号为PG2L100H-6FBG676

将瑞苏盈科Mercury+ XU1与Klepsydra AI相结合,可以使用卫星传感器数据实现实时、高精度定位

FPGA与RISC-V架构的结合为创新应用开启了一个新纪元,随着边缘计算、自动驾驶、数据中心等领域的快速发展,对计算性能和灵活性的需求越来越高

UVHS支持第三代昆明湖16核CPU突破验证挑战,携手探索下一代HPC验证新范式

在设计RFSoC PS时,必须选择合适的软件堆栈来满足设计要求。软件栈是一组基本软件,开发人员可以在这些软件的基础上添加他们自己的定制软件