【XDF资料下载】基于 FPGA 的加速原理

judy 在 周三, 01/09/2019 - 10:42 提交

基于 FPGA 的加速原理

基于 FPGA 的加速原理

很多使用ZCU106/104开发板的小伙伴,发现在官网上可以找到包括IPI,MIG,PCIe等参考设计,但是如何把VCU用起来的流程设计,Target Reference Design(以下简称TRD)不知道哪里去下,那么最新版本的TRD去哪里获得呢?

一、用HLS生成一个定制IP(加速器)

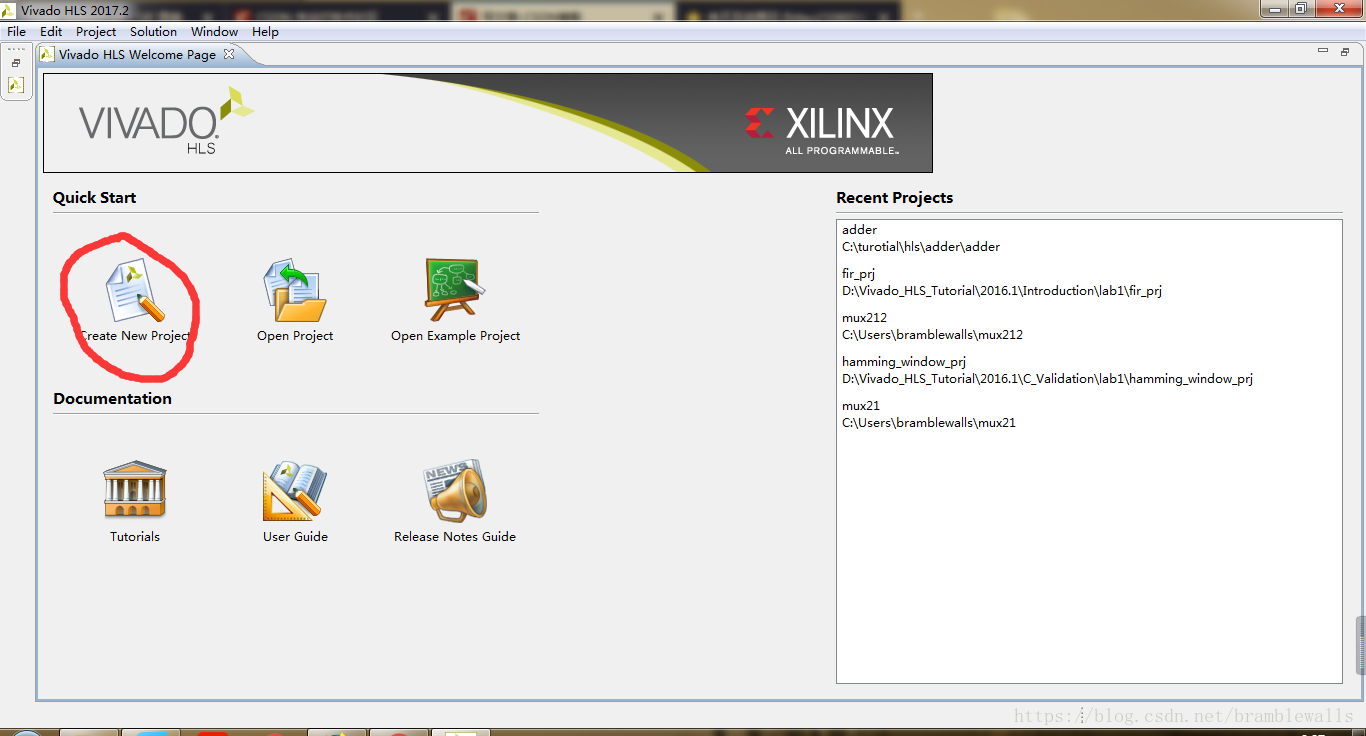

(1)首先打开vivado hls,本人的版本是2017.2,点击创建一个新工程。

(2)设置工程名和路径,顶层函数设置为add,创建一个新的C++程序,名字叫做adder.cpp,不用在testbench中添加文件。

选择板子的时候搜索xc7z020clg400-1,这是PYNQ的板子号,选择完成。

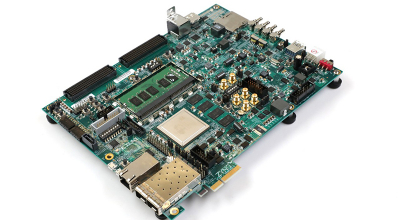

视频演示了 DDR3 内存的 Kintex-7 FPGA 接口功能。

前面我们介绍了按键中断,其实我们稍作修改就可以用按键控制LED了。做个小实验,两个按键分别控制两个led亮灭。

板子:zc702。

硬件部分

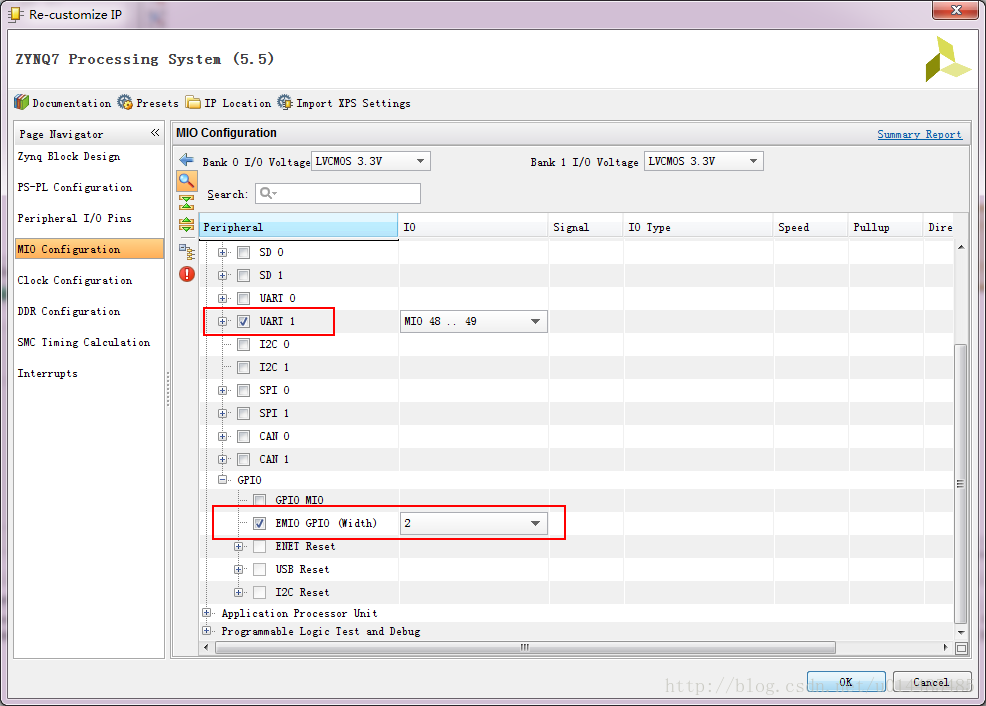

添加zynq核:

勾选串口用于打印信息,勾选EMIO,我们控制两个led,所以需要2bit

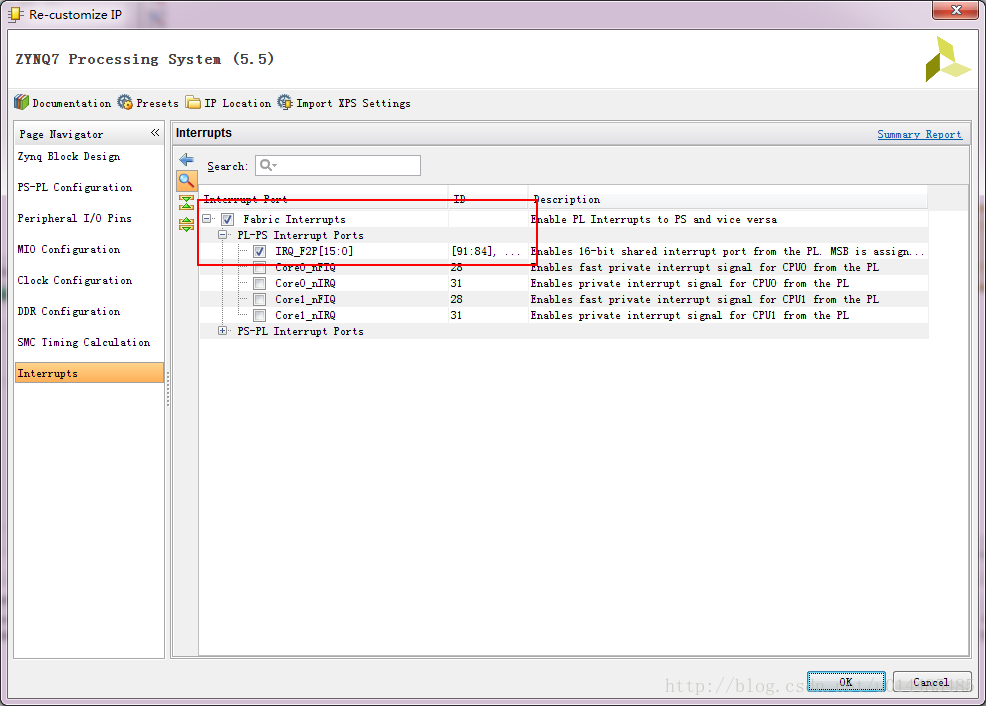

PL 到PS的中断勾选上:

PL时钟什么的都用不到,我们用的按键不需要时钟,EMIO属于PS。

再添加一个concat IP用于合并两路按键信号:

为了复用现有的MATLAB®代码,LabVIEW Communications System Design Suite (LabVIEW Comms) 新增了MATLAB专用接口的功能。无线原型的开发者可使用已有的MATLAB函数或脚本,将其连接至LabVIEW Comms在Windows处理器上运行的代码部分

计算机视觉在汽车、医疗、消费和农业市场的发展势头迅猛。由于与机器学习相结合的计算机视觉技术的高速演进,团队需要一种方法,用于在规范和要求演进的同时设计和验证算法,而无需在每次出现变化时重新开始设计。要想成功地开发这些系统,唯一的方法是使用 High-Level Synthesis。

vivado自带很多命令帮助编译器更好的实现设计者的想法,用得好会变成开发利器。比如,max_fanout命令,本身是用来约束扇出,减少布线拥塞的常用命令。然而很多读者向我反映,使用这个命令之后发现没有任何事情发生,完全没有任何效果。这里我就带大家理一理这个命令的使用方法

Xilinx 在 XDF Silicon Valley 2018 上展示了 Alveo U250 加速卡上的 ML 套件

赛灵思公司与采埃孚股份公司 (ZF) 今天联合宣布开展一项全新战略合作,赛灵思将通过为 ZF 高度先进的人工智能 (AI) 汽车控制单元 ZF ProAI 提供支持,加速促成无人驾驶应用落地。ZF 正在使用赛灵思 Zynq® UltraScale+™MPSoC 平台处理实时数据汇总、预处理和分配,同时也为其 AI 全新电子控制单元的 AI 处理提供计算加速