赛灵思最新深度神经网络推理器xDNN参数曝光

judy 在 周三, 08/29/2018 - 13:17 提交

继年初发布新一代FPGA框架后,FPGA巨头赛灵思在Hot Chips大会揭露了最新一代深度神经网络推理装置xDNN的部分规格参数。随着更多定制芯片的发展,现如今AI芯片的战火已经蔓延到推理领域。赛灵思的xDNN可配置、可复写,进行多任务处理,还配有Tensor内存。

继年初发布新一代FPGA框架后,FPGA巨头赛灵思在Hot Chips大会揭露了最新一代深度神经网络推理装置xDNN的部分规格参数。随着更多定制芯片的发展,现如今AI芯片的战火已经蔓延到推理领域。赛灵思的xDNN可配置、可复写,进行多任务处理,还配有Tensor内存。

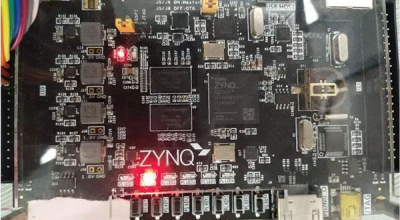

本系列第13篇简单介绍了使用RTL工程IO布局工程两种方法定义IO Ports。在I/O Planning View Layout中(IO布局工程中是Default Layout),显示了FPGA器件资源、封装管脚、I/O Ports等详细信息。设计者借助这些信息来完成I/O规划。

简介

学习PCIe有一段时间了,这里将这段时间的学习做一个总结。由于手里没有包含PCIe的板子,因此所做的也就是尽力将XILINX提供的实例工程中的关键模块进行分析,包括 PIO_RX_ENGINE.v,PIO_TX_ENGINE.v,PIO_EP_MEM_ACCESS.v ,希望对和我一样的初学者有所帮助。

本文主要介绍如何使用 HSI 工具来创建一个定制驱动程序,使 xparameters.h 文件驻留在 SDK 中。

第 1 步:在 IP 打包器中创建 IP

在以下实例中创建一个简单的 AXI 从 IP 并连接至 MPSoC 器件:

本文是该系列的第13篇。Vivado HLS是Xilinx FPGA开发套件中的一款软件,可以使用C/C++语言进行设计,并转换为RTL级模型。System Generator中的Vivado HLS block可以将HLS开发软件设计的C/C++代码整合到Simulink环境中,利用Simulink强大的仿真特性对设计进行仿真测试。

作者:OpensLee,FPGA开源工作室

作者:作者:德州仪器 Chris Glaser

随着电子设备的尺寸越来越小,电源设计人员在设计电源时必须考虑热限值的问题。如果一个较小的电源无法在特定的应用环境(包括环境温度)下以高负载运行,那么它就等同于没有用处。

无线通信是现在应用最为广泛的通信技术之一,其核心是把要传输的数据调制在载波上发射出去,载波状态的变化承载了不同的信息。

近日,Xilinx主管全球数据中心业务的副总裁Freddy赴深访问恒扬数据总部,Freddy 一行在CEO李浩等高层的陪同下,对恒扬数据进行了深入调研和参观,双方在愉快的气氛中对以往业务进行了梳理,并达成进一步深化合作意向,双方均对未来合作充满期待。

作者:卢佳柔,新通讯 2018 年 9 月号 211 期《 行家出手 》