PyTorch快速微调量化的一个例子

judy 在 周一, 02/21/2022 - 17:26 提交

训练好的模型在部署过程中的Vitis AI转换过程要经过优化、量化和编译等步骤。尤其是量化,可以通过三种不同的方式实现。

训练好的模型在部署过程中的Vitis AI转换过程要经过优化、量化和编译等步骤。尤其是量化,可以通过三种不同的方式实现。

从傅里叶变换到小波变换,并不是一个抽象的东西,完全可以讲得很形象。小波变换有着明确的物理意义,如果我们从它的提出时所面对的问题看起,可以整理出非常清晰的思路

时钟信号在很大程度上决定了整个设计的性能和可靠性,尽量避免使用FPGA内部逻辑产生的时钟,因为它很容易导致功能或时序出现问题

本文提供有关使用 Zynq® UltraScale+™ MPSoC 的产品的 FIPS 140-3 认证的入门知识。

本文将指导用户,如何使用第二种方式产生的例子工程,添加自己的数据激励,用于完成自己所需要的仿真验证

BEL是最底层的基本元素,也可以叫atomic unit(原子单位),BEL是FPGA中最小、不可分割的组件。BEL有两种:Logic BEL和Routing BEL。

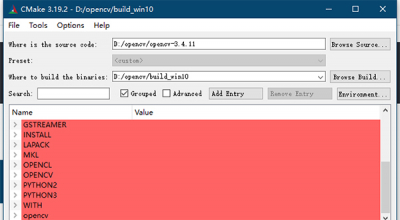

Vitis HLS OpenCV库编译

所有工具和参考设计使用2021.2。编译和测试X86主机(Host)的操作系统是CentOS 7.9.2009。测试的单板是VCK190,测试的是CPM QDMA。

提供给7系列FPGA收发器中PLL的参考时钟的质量可以极大地影响发送抖动和接收抖动容限的性能。参考时钟的抖动或相位噪声在决定这种性能方面起着重要作用--相位噪声是首选的规范方法

如图所示, 源文件目录中haha文件夹下有一个hoho.h头文件。本来要包含这个头文件应该写成#include "haha/hoho.h"的,但是如果写成#include