AMD Xilinx 助力打造超低时延的高频金融交易平台

judy 在 周五, 06/17/2022 - 12:18 提交

本次直播会议我们邀请到了来自 AMD 以及我们的合作伙伴的金融行业专家,共聚一堂与您分享AMD Xilinx 如何满足金融行业对超低时延的需求,以及面向高频交易的加速方案

本次直播会议我们邀请到了来自 AMD 以及我们的合作伙伴的金融行业专家,共聚一堂与您分享AMD Xilinx 如何满足金融行业对超低时延的需求,以及面向高频交易的加速方案

在数字电路中存储单元有两种,一种是触发器,一种是锁存器。它们两者最大的区别是:前者通过时钟沿到来改变存储的输出状态,后者是通过电平变换来改变存储的输出状态。

近日,AMD举行2022年金融分析师日活动,在活动中公司高管表示,AMD拥有适合的芯片和软件在更广泛的AI领域开拓疆土。

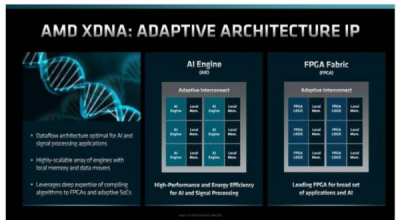

本文档涵盖了以下设计进程:系统和解决方案规划,即确认系统级别的组件、性能、I/O 和数据传输要求,包括解决方案到 PS、PL 和 AI 引擎的应用映射。

随着 AMD 起航以制造更符合客户喜好的产品,AMD打开了芯片新大门。详细介绍了模块化芯片的未来,客户可以在定制芯片封装中混合和匹配非 AMD 处理器。

FPGA与STM32等嵌入式开发最大的一个优点就是,可以在时序仿真阶段验证超过90%的功能,发现90%的问题

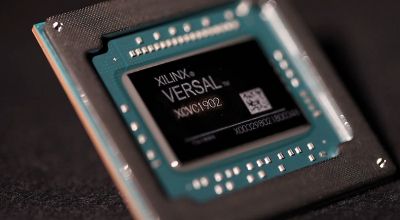

本视频介绍了此版本中的新功能和增强功能,包括 Versal® 设计的结果质量 (QoR) 改进、基于 ML 的资源估计、面向 Versal 器件的 ML 策略运行以及其他器件支持。

在Zynq MPSoC的器件里,PS (Processing System )集成了三个看门狗,分别是CSU SWDT,LPD SWDT和FPD SWDT。CSU SWDT用于保护CSU与PMU及其相关连接。

多路选择器MUX是一个多输入、单输出的组合逻辑电路,一个n输入的多路选择器就是一个n路的数字开关,可以根据通道选择控制信号的不同