如何生成BRAM初始值的coe文件?

guanxiao_505740 在 周五, 07/01/2022 - 09:30 提交

Vivado中BRAM IP核是经常会用到的,而一种比较简便的给RAM赋初值的方式就是通过一个coe文件进行加载,那么如何用matlab来产生这样一个可直接使用的coe文件呢?

Vivado中BRAM IP核是经常会用到的,而一种比较简便的给RAM赋初值的方式就是通过一个coe文件进行加载,那么如何用matlab来产生这样一个可直接使用的coe文件呢?

Kria™ KR260机器人入门套件包括用于机器人、机器视觉、工业通信和控制应用的预建接口、可定制的硬件加速功能,并通过Kria SOM加快部署时间。

Imagination的 IMG RTXM-2200 加快了公司RISC-V产品的扩展速度。它可以集成到复杂的系统级芯片(SoC)中,应用范围包括网络解决方案、数据包管理、存储控制器、用于AI摄像头和智能计量的传感器管理等。Imagination的这款全新CPU核与其领先的GPU和AI加速器IP一起为客户提供创新的异构解决方案。

要点概览:

Block_RAM应该是每个FPGA开发者经常遇到的,其作为一种固定资源存在于FPGA中,针对xilinx的BRAM,正常通过vivado的IP Core Generator得到

本文将告诉你:对于小型设计,要如何编写一个高效率的testbench。

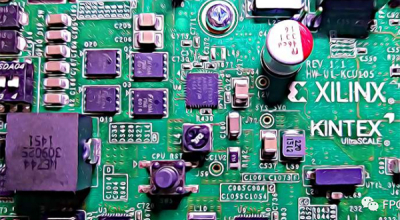

本视频教程阐述了如何创建一个Vivado工程,以及如何基于VHDL设计案例和EV12AQ600-ADX-EVM演示板,在Kintex Ultrascale FPGA上实现ADX4 IP。

Versal AI Core 系列具备的高性能和超低时延处理能力显著缩短了图像处理时间,与传统架构的几分钟时间相比,这种架构能够近乎实时地生成直播回放

本文旨在帮大家了解如何在运行 Ubuntu 桌面的 Xilinx KV260 Vision AI 入门套件上轻松设置机器学习推理功能。

之前很早就听说了FSMC接口用于MCU与FPGA之间的通讯。最近使用的一款MCU与FPGA之间通讯,FPGA模拟成NAND Flash作为Memory让MCU读写

我们将介绍使用 Vivado 硬件管理器对开发板闪存进行编程的步骤。