如何在Block diagram中为PR区域添加.bd格式的Reconfigurable Module

judy 在 周四, 07/07/2022 - 14:26 提交

关于DFX的问题: 正在尝试为Xilinx Github下的PYNQ_Composable_Pipeline工程的PR_0区域添加新的RM(Reconfigurable Module)

关于DFX的问题: 正在尝试为Xilinx Github下的PYNQ_Composable_Pipeline工程的PR_0区域添加新的RM(Reconfigurable Module)

本文描述了K26 SOM载体卡热设计的最佳实践。

本节我们介绍以下知识点:SelectIO资源概述及结构,SelectIO管脚通用设计指导。

在有些情况下,开发人员只有综合后的DCP文件和对应的约束XDC及各个IP,并没有综合之前的code,这种情况下vivado可以通过tcl脚本跑完实现并得到bit。

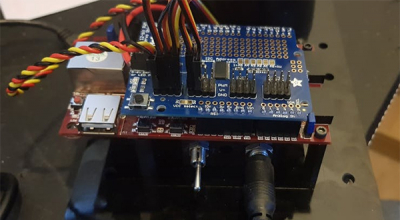

本示例将使用在Zynq SoC的控制下使用六个伺服器的机械手。它可以使用简单的软件界面或使用两个Pmod操纵杆进行直接控制来进行控制。

本人比较喜欢Xilinx家的东西,这里就讲一讲Xilinx家的MIPI方案。这里以普通7系列作为讨论的对象

本文将对RAM IP核的各个关键因素做详细的讲解。

xkISP 是基于 Xilinx HLS 的开源图像信号处理器 (ISP)。xkISP由复旦大学VIP实验室和阿里巴巴DAMO CTL实验室联合开发