(更新)什么样的电脑配置跑Vivado FPGA综合最快?

judy 在 周三, 07/27/2022 - 10:38 提交

12代酷睿CPU在win10、11下一些问题经过的解决方法(经过实践的)

12代酷睿CPU在win10、11下一些问题经过的解决方法(经过实践的)

array命令:可以查询一个数组变量中已经定义的元素的信息。

本文主要是和DDR的对比,对项目前期的选型做一分析。

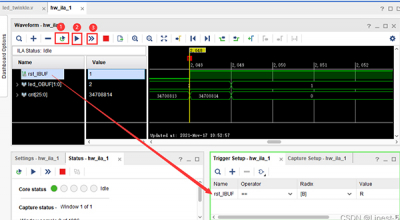

FPGA综合出来的电路都在芯片内部,基本上是没法用示波器或者逻辑分析仪器去测量信号的,所以xilinx等厂家就发明了内置的逻辑分析仪

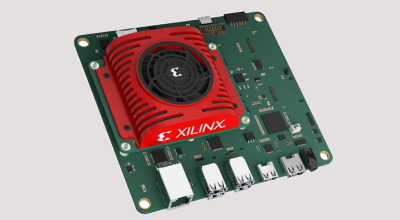

在KV260单板中有一个IIC控制的4选1路开关芯片TAC9546A,使用时通过IIC设置该芯片选择IIC通道,PS中输出一路IIC可以控制4路IIC设备。

这篇文章主要是通过介绍7系列与之前产品的对比,来展示7系列产品的基本逻辑单元的优点。

tcl脚本提供了错误和异常处理机制,error可以看做是异常的特例,毕竟导致脚本被终止,除了error还有break、continue、return等。

在上一篇关于HBM的介绍中,详细介绍了HBM的架构和配置,这里再记录下HBM另一个重要的特性——性能。

Xilinx 7系列FPGA具有灵活的内部存储资源架构,可以可配置为各种不同的尺寸。本文详细解释了这一特性,并阐述了如何进行资源与性能之间的权衡取舍。

利用 UART IP 以及 AXI Interrupt Contriller IP 实现通过串口发送数据产生中断,控制器接收到中断并将串口发送出来的数据重新通过串口打印出来