【Vivado那些事儿】设计分析报告

judy 在 周四, 02/29/2024 - 10:09 提交

实现 FPGA 设计最耗时的要素之一通常不是设计,而是实现想要的时序性能

实现 FPGA 设计最耗时的要素之一通常不是设计,而是实现想要的时序性能

本文将详细介绍饱和度调节的知识、常用的算法以及FPGA实现。

Vivado提供了丰富的IP库,以下是一些常见的Vivado IP

在 FPGA上的 Ubuntu 22.04 桌面映像上安装了各种 EE 设计应用程序

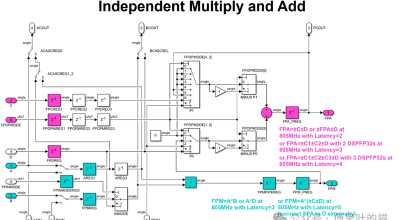

本文将重点介绍其中的DSPFP32,它是一个硬化的浮点加法器和乘法器

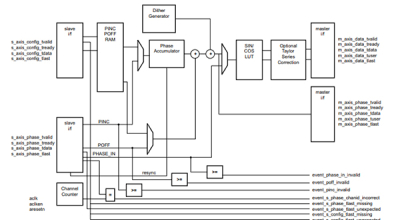

直接数字合成器或数控振荡器是许多数字通信系统中的重要部件

ISP的功能可以简单概括为使后端能正确识别“真实的”世界

PCIe core往往是硬core,实现PCIe的物理层、链路层和事务层

Forwarded Clock是一种时钟信号管理技术,用于在不同部件之间同步数据和控制信号

本文以ZU11EG为例介绍,如何进行对应的硬件引脚分配。