Xilinx DDR3学习总结——4、添加读写功能

judy 在 周二, 09/19/2023 - 10:33 提交

前面modelsim已经仿真成功了DDR3的初始化

前面modelsim已经仿真成功了DDR3的初始化

有一个数据需要从A时钟域同步到B时钟域,数据位宽是512bit的

本文将介绍如何清理Vivado工程,并避免缺失必要的文件。

本文将要介绍一下Vivado的综合参数设置

在生成example的时候,vivado就自带仿真激励的

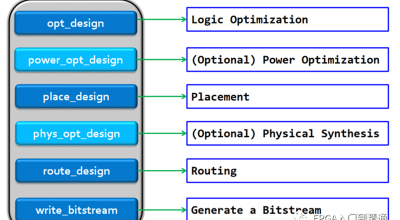

本文主要介绍Vivado布线参数设置

AMD 128核心/256线程EPYC 9754处理器独家测试

异步FIFO通常用于跨时钟域处理,是逻辑设计常用基础模块

本文将介绍Vivado增量编译的基本概念、优点、使用方法以及注意事项

查看MIG IP输出的init_calib_complete信号