Serdes系列总结——Xilinx serdes IP使用(二)——10G serdes

judy 在 周二, 08/09/2022 - 14:53 提交

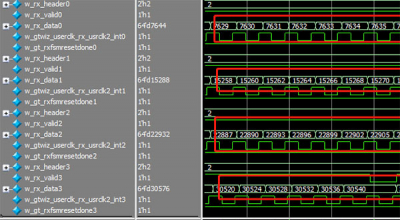

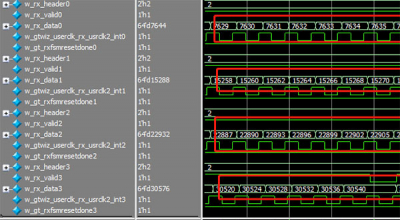

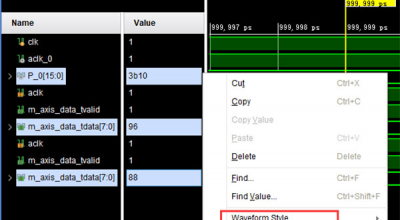

10.1376G的serdes,一个输入为64bit,输出为64bit的6664B编码的4对serdes例程,参考时钟为153.6MHz

10.1376G的serdes,一个输入为64bit,输出为64bit的6664B编码的4对serdes例程,参考时钟为153.6MHz

在FPGA的设计里,RR(Round-Robin)调度是一个非常重要的话题。所谓RR调度就是从多个队列中公平地选一个队列进行处理。

本实验要完成利用vivado中的DDS IP核对两个正弦波进行混频,实现数字下变频或者上变频。

一个线速率为3.072G的,输入为20bit,输出为20bit的无协议无编码的4对serdes例程,参考时钟为153.6MHz

接口综合有两种,一种是block-level interface protocol和port-level interface protocol。

让我们以一个简单的例子,FIR 滤波器,来看看如何写出能适配不同型号 FPGA 的代码。

在FPGA的时序分析页面,我们经常会看到Max at Slow Process Corner和Min at Fast Process Corner,具体是什么含义呢?

本文基于可编程晶振SI570,就Xilinx FPGA收发器输入参考时钟的硬件设计及FPGA软件设计给出设计案例,供大家参考

在最近的工作中,又遇到了丢包逻辑的设计。突然想到在FPGA设计中,这是一个非常常见的功能,所以做一个简单的总结。

本教程涉及到linux版本下安装vivado(vitis)、qt和petalinux的安装。