FIFO 最小深度计算

judy 在 周二, 08/23/2022 - 09:22 提交

当我们需要在两个模块之间进行数据的传输,并且两个模块的时钟是不同的,当一定数量数据传输时为了避免数据出现丢失

当我们需要在两个模块之间进行数据的传输,并且两个模块的时钟是不同的,当一定数量数据传输时为了避免数据出现丢失

在FPGA开发设计中,我们可能会经历由于资源占用过高的情况,例如BRAM、LUT和URAM等关键资源利用率达到或超过80%

在光纤通信开发中,ibert ip会经常用到,它不但可以用来测试误码,测试眼图,还可以通过调整参数使眼图达到比较理想的状态。

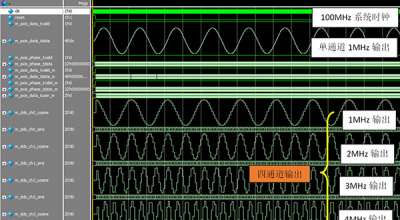

本文我们通过例化Xilinx公司的DDS IP核来产生混频器本振输入频率,并给出Modelsim仿真测试结果。

MIG IP控制器是Xilinx为用户提供的一个用于DDR控制的IP核,方便用户在即使不了解DDR的控制

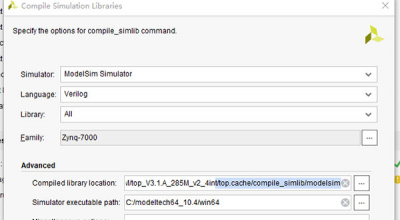

如果只是纯的.v文件仿真那很容易操作,主要是涉及到IP核,那么就必须要对vivado的IP核的库文件进行编译

在FPGA的设计中的DFX主要是包括可测试性设计和可维护性设计这2大点。最终的目的是快速定位板上问题和后期维护阶段日常巡检诊断。

该系列的第二部分描述了一种可能的双时钟设计的架构。在第三部分中,我们将探索另一种选择双时钟 FIFO 架构

一片RAM中分为许多小格,每一片容量为36k,根据设定的位宽决定了这片RAM可以存放分为几格

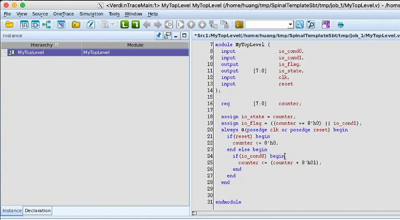

本篇文章来源于微信群中的网友,分享下在SpinalHDL里如何丝滑的运行VCS跑Vivado相关仿真。