Vivado之ILA详解

judy 在 周二, 01/05/2021 - 11:04 提交

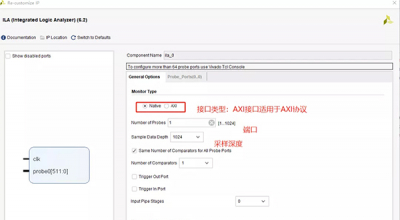

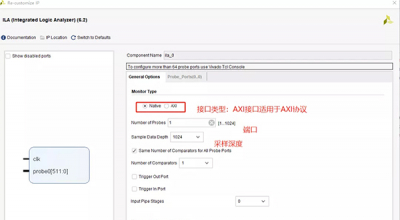

集成逻辑分析仪 (Integrated Logic Analyzer :ILA) 功能允许用户在 FPGA 设备上执行系统内调试后实现的设计。当设计中需要监视信号时,应使用此功能。用户还可以使用此功能在硬件事件和以系统速度捕获数据时触发。

集成逻辑分析仪 (Integrated Logic Analyzer :ILA) 功能允许用户在 FPGA 设备上执行系统内调试后实现的设计。当设计中需要监视信号时,应使用此功能。用户还可以使用此功能在硬件事件和以系统速度捕获数据时触发。

PYNQ框架的设计初衷是通过高层次的封装,将底层硬件FPGA实现细节与上层应用层的使用脱耦,对软件开发者来说,PYNQ框架已经提供了完整的访问FPGA资源的library,让上层应用开发者通过Python编程就可以调用FPGA模块,不需要懂Verilog/VHDL硬件编程就可以享受FPGA可并行计算、接口可方便扩展和可灵活配置带来的诸多好处

图像在采集和传输的过程中,通常会产生噪声,使图像质量降低,影响后续处理。因此须对图像进行一些图像滤波、图像增强等预处理。为改善图像质量,去除噪声通常会对图像进行滤波处理 ,这样既能去除噪声,又能保持图像细节。

并不局限于Vivado一种EDA。头文件主要使用“文件包括”处理,所谓"文件包含"处理是一个源文件可以将另外一个源文件的全部内容包含进来,即将另外的文件包含到本文件之中。Verilog语言提供了`include命令用来实现"文件包含"的操作。

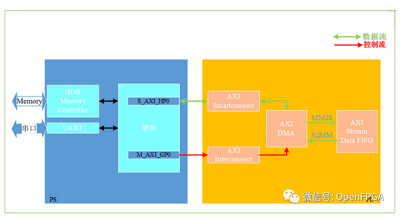

DMA中断实例化函数,将要配置的DMA信息先lookupConfig再进行CfgInitialize,DMA采用块模式(Block mode),如果是Sg模式,则配置失败。定时器初始化函数,传入参数有定时器结构、加载值,设备ID。

本文介绍如何一步一步将设计从SDSoC/Vivado HLS迁移到Vitis平台。

完成Implementation后,在Vivado IDE左侧的Flow Navigator点击Open Implemented Design,然后点击report_utilization。

Xilinx-7系列FPGA主要包括:Spartan®-7、Artix®-7、Kintex®-7、Virtex®-7。其性能、密度、价格也随着系列的不同而提升。和前几代FPGA产品不同的是,7系列FPGA采用的是统一的28nm设计架构,客户在不同子系列的使用方式上是统一的,消除了不同子系列切换使用带来的不便。当然Kintex®-7、Virtex®-7两个系列后续还有20nm和16nm设计架构。

FDRE代表一个单D型触发器,含的有五个信号分别为: 数据(data,D)、时钟使能(Clock enable,CE)、时钟(Clock)、同步复位(synchronous reset,R)、数据输出(dataout,Q)。当输入的同步复位信号为高时,否决(override)所有输入,并在时钟的上升沿将输出Q为低信号。

增加一个AXIDMA章节,这部分内容是很多例程的基础,难度不大但是也不小,需要彻底理解整个运行机制。