基于TCP/IP协议的电口通信

judy 在 周五, 06/05/2020 - 16:18 提交

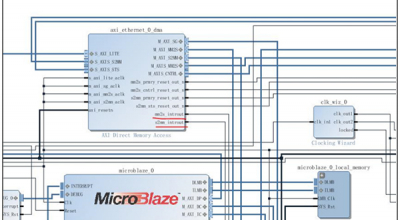

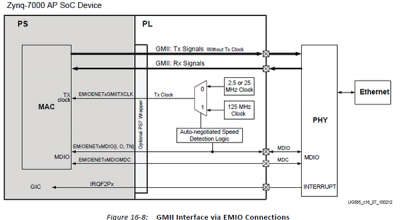

LWIP可以通过硬核实现或者软核实现,具体要看FPGA的选型,其中硬核可以通过硬核自带的GMAC通过直连PHY或者EMIO扩展到PHY都可以实现相应功能,同时硬核也可以通过AXI总线与相应的IP相连然后再同外部PHY连接实现相应功能。这部分Xilinx官方提供详细的文档xapp1306-ps-pl-ethernet-performance-lwip和测试例程

LWIP可以通过硬核实现或者软核实现,具体要看FPGA的选型,其中硬核可以通过硬核自带的GMAC通过直连PHY或者EMIO扩展到PHY都可以实现相应功能,同时硬核也可以通过AXI总线与相应的IP相连然后再同外部PHY连接实现相应功能。这部分Xilinx官方提供详细的文档xapp1306-ps-pl-ethernet-performance-lwip和测试例程

在VIVADO的实现的布局中,可以利用PBlock将某一个或某几个Cell(模块单元)固定在Device的固定区域上。如此,可以实现该模块内部的时序收敛,并且,该工具对于可重配置工具的使用也是必不可少的

lwip 是瑞典计算机科学院(SICS)的 Adam Dunkels 开发的一个小型开源的 TCP/IP 协议栈。实现的重点是在保持 TCP 协议主要功能的基础上减少对 RAM 的占用。LwIP 是 Light Weight (轻型)IP 协议,有无操作系统的支持都可以运行。LwIP 实现的重点是在保持 TCP 协议主要功能的基础上减少对 RAM 的占用,它只需十几 KB 的 RAM 和 40K 左右的 ROM 就可以运行

GTX是kintex-7系列FPGA内部的高速数据收发器硬核模块,专门用于FPGA与外部的高速数据通信,目前许多常用的高速协议(比如JESD204、PCIE、SATA、SGMII接口的以太网等)的实现都需要用到GTX。GTX的基本内容以前介绍过了,这里不再叙述。该篇主要记录两片FPGA利用各自的GTX实现高速数据的收发过程

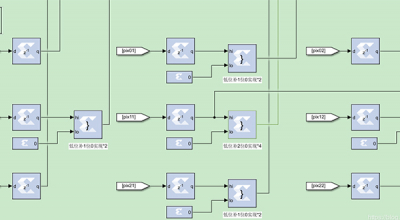

本例程将 PS 的 ETH1 通过 EMIO 方式引出, 通过 EMIO 引出的 ETH 为 GMII 接口, 将其与 GMII to RGMII IP 核连接后转换成 RGMII 接口,然后与外部子卡中的 88E1512 芯片连接。在 PS 端通过 SDK 自带的 lwip echo server 例程通过子卡,以 RJ45 电口与 PC 机实现 TCP 网络通信

通过上面其他章节的介绍,网口千兆通信,可以使用TCP或者UDP协议,可以外挂PHY片或者不挂PHY片,总结下来就有下面几种方式完成通信

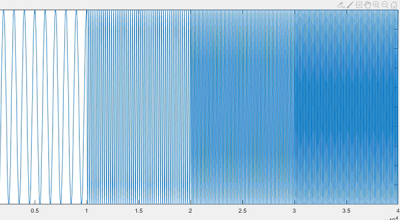

在Matlab中,做短时傅里叶变换需要使用函数spectrogram,而在Matlab2019中,引入了一个新的函数stft,下面我们就来看下这两个函数都如何使用。

首先通过上面的简单分析,我们应该很清楚一件事:TCP协议很复杂,光握手过程就需要“三次握手、四次挥手”的复杂过程,不是特别适合FPGA的纯逻辑实现,因为用FPGA实现以太网通信的主要目的就是进行低延时的传输数据,而一旦设计规模达到一定量级,FPGA实现通信的优势便不复存在,转而体现出“性价比”低的劣势

为什么UDP协议在FPGA实现时很受欢迎,最主要一个原因就是简单,简答到什么地步呢?UDP协议只是在IP的数据服务之上增加了复用和分用的功能和查错检验的功能。

锐化即在图像上增强显示图像内容的边缘成分。根据边缘成分的计算方法,常用的方法有高斯滤波锐化和拉普拉斯滤波锐化。高斯滤波锐化将原始图像 x 减去高斯滤波(相当于低通滤波)后得到的平滑图像 gaussian(x)