千兆以太网(4):发送——ODDR原语和Wireshark抓包工具

judy 在 周四, 05/14/2020 - 14:35 提交

FPGA 传输的数据为单沿数据,而 PHY 传输的数据为双沿数据,所以FPGA 发送心跳包的最后需要使用 ODDR 原语将单沿数据转换为双沿数据。通常情况下 FPGA 处理数据使用的时钟为晶振产生的时钟(FPGA 时钟),而 FPGA 传输来的数据经过ODDR 原语后转换为双沿的数据都是和 PHY 的时钟同步

FPGA 传输的数据为单沿数据,而 PHY 传输的数据为双沿数据,所以FPGA 发送心跳包的最后需要使用 ODDR 原语将单沿数据转换为双沿数据。通常情况下 FPGA 处理数据使用的时钟为晶振产生的时钟(FPGA 时钟),而 FPGA 传输来的数据经过ODDR 原语后转换为双沿的数据都是和 PHY 的时钟同步

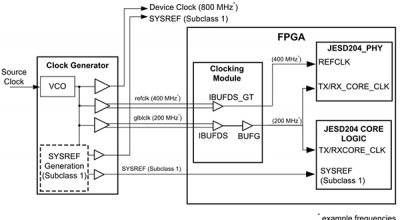

本篇的内容基于jesd204b接口的ADC和FPGA的硬件板卡,通过调用jesd204b ip核来一步步在FPGA内部实现高速ADC数据采集,jesd204b协议和xilinx 的jesd204 IP核相关基本知识已在前面多篇文章中详细介绍,这里不再叙述~

心跳包就是在客户端和服务器间定时通知对方自己状态的一个自己定义的命令字,按照一定的时间间隔发送,类似于心跳,所以叫做心跳包。心跳包在GPRS通信和CDMA通信的应用方面使用非常广泛。数据网关会定时清理没有数据的路由,心跳包通常设定在30-40秒之间。所谓的心跳包就是客户端定时发送简单的信息给服务器端告诉它我还在而已

Petalinux2019.1的安装与之前大体类似,但是有几个小坑,再次记录一下。

直方图均衡算法通过将各颜色通道的像素点数值间距拉大,实现在当前颜色通道内像素点数值的大幅差异,增强视觉效果。除此以外,在图像传感器输入的像素值位宽与实际用于显示的像素值位宽不一致的情况下,直方图均衡算法也常用于像素点位宽的转换

本篇介绍AXI4-Lite接口协议的数据读写操作~

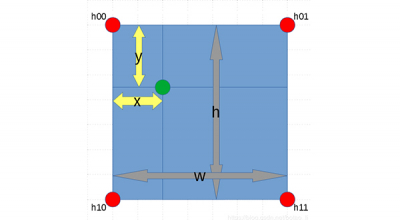

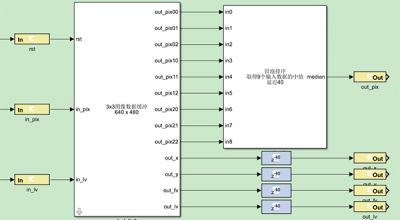

中值滤波是一种算法简单,效果较好的“高性价比”去噪算法。算法原理是使用图像内二维滑窗的中值(全部像素点数值排序位于中间位置的数值为中值)代替当前像素点值。如下图的 3×3滑窗内,处于滑窗中心的当前像素点值为 8,滑窗内全部 9 个像素点的中值为 5

很多工程师都会选择多个jobs进行编译,以为这样会更快一些,而且这个jobs的数量跟本地CPU的线程数是一致的,这就更加让工程师们认为这个选项就是多线程编译了。但对Vivado更加熟悉的工程师,肯定会知道,Vivado中的多线程是通过tcl脚本去设置的,而且目前最大可使用的线程数是8个,那这个jobs跟多线程有什么关系呢?

前面我们实现了FPGA板卡接收以太网的数据,但是里面的数据比较乱,而且可能出现无效帧,即便是有效帧,也不是所有数据都是我们要的,必须对数据进行筛选。本篇博客详细记录一下以太网数据的校验和筛选。

本篇参考xilinx官方JESD204 IP核的数据手册PG066,具体介绍基于该IP核的JESD204B数据传输实现方法~