hash算法在FPGA中的实现(二)——hash链表

judy 在 周一, 06/12/2023 - 09:37 提交

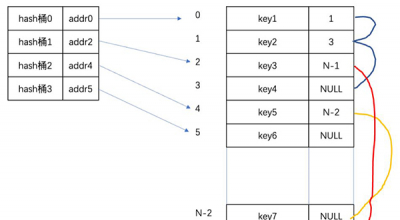

这里介绍两种常见的设计hash链表的方案

这里介绍两种常见的设计hash链表的方案

本文简单介绍了AD9129的基础知识,包括芯片的重要特性

今天的文章让我们来看看当设计不能满足时序要求时如何分析并解决它

本文我们介绍下Xilinx DDR3 IP核的重要架构、IP核信号管脚定义、读写操作时序

ROM的英文全称为Read-Only Memory,即只读存储器。可以从任意地址上读取数据

该项目介绍了如何使用 Verilog 实现具有预生成系数的简单 FIR 滤波器。

在FPGA的设计中,尤其是在通信领域,经常会遇到hash算法的实现

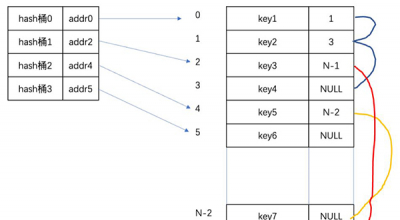

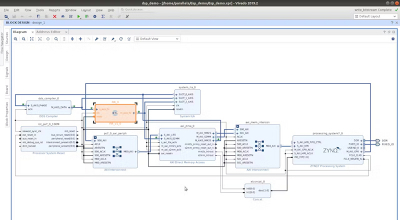

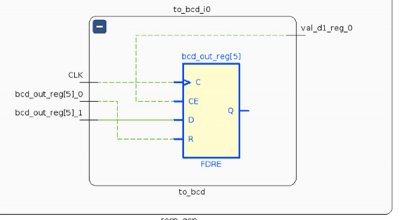

Vivado Schematic中的实线和虚线有什么区别?以下图为例

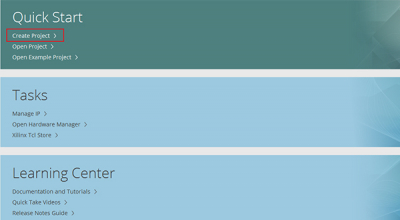

本文介绍如何创建Golden镜像和Multiboot镜像,以及加载失败Fallback回退的原理。

新型VPX(VITA 46)标准是自从VME引入后的25年来,对于VME总线架构的最重大也是最重要的改进