ZYNQ学习之路——在SDx中使用xfOpenCV图像加速处理

judy 在 周五, 11/12/2021 - 10:18 提交

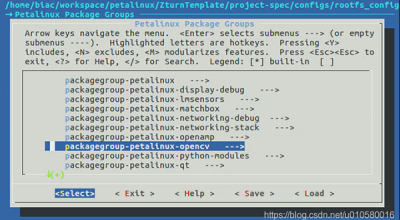

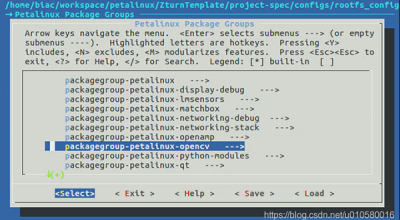

本文以Zturnboard为例介绍如何在SDSoC中使用OpenCV,本文在Ubuntu 16 64位,SDSoC2018.2(安装在ubuntu中)中测试通过。

本文以Zturnboard为例介绍如何在SDSoC中使用OpenCV,本文在Ubuntu 16 64位,SDSoC2018.2(安装在ubuntu中)中测试通过。

虽然看起来AXI Interrupt Controller的intr[0:0]位宽无法修改,但实际上,添加一个Concat IP,这个IP可以设置In0的个数,设置为2。In0连接上中断线后,再把dout和intr相连

在FPGA的开发中,对于两个异步时钟,如果我们可以在RTL的设计中保证这两个时钟域之间的处理都是正确的,那就可以让工具不分析这两个时钟域之间的交互。

在第三节中,我们成功创建了ZYNQ裸机下的SDSoC平台文件,但在实际使用中,要求使用Linux操作系统。本节介绍如何创建基于Linux系统的硬件平台。

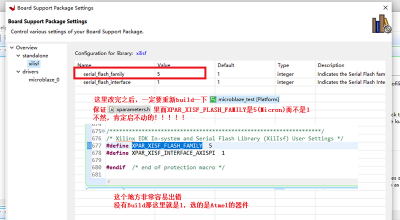

本教程以米联客XC7A35T FGG484-2开发板为例,详细讲解一下用Xilinx Vivado 2020.1创建MicroBlaze软核工程,然后再用Xilinx Vitis 2020.1建立Hello World C程序工程的完整操作步骤。

在完成PYNQ环境搭建后(zynq7035单板创建PYNQ镜像V2.6),本文介绍如何在PS端进行图片缩放。

对于Xilinx的FPGA,每一片都有一个专门的ID,就像我们的身份证号一样,每个都不一样,Xilinx也形象的把这个ID叫做DNA。7系列以及之前FPGA的DNA有57bit,Ultrascale FPGA的DNA有96bit,Zynq Ultrascale+的FPGA有两个DNA,PL端一个,PS端也有一个。

FPGA的型号为XC7A35TFGG484-2,开发板用的是米联客的。主程序hello_world运行于外部DDR3内存,SREC SPI Bootloader运行于FPGA片内BRAM。

在前面的学习中,我们已经学会了使用Vivado及SDK开发环境,熟悉了硬件开发与Linux软件驱动之间的联系及开发流程。本系列教程我们学习SDSoc的开发,在SDSoc IDE中,Xilinx为我们集成了比较流行的开发板硬件平台,如果我们使用的是其中的一个,可以直接使用。但笔者使用的是米尔科技的7z010开发板,在开发之前首先要定义我们自己的硬件平台,作为之后创建应用的模板工程

本节教程介绍如何使用SDSoC软件创建硬件平台,并且使用它来加速程序函数。