FPGA中截位导致的直流分量如何去除?

judy 在 周二, 10/12/2021 - 14:37 提交

在用FPGA做算法时,由于FPGA中一般都是使用定点数据,因此经常需要移位操作。比如一个16bit的信号经过滤波器后,由于滤波器的增益,输出结果肯定不是16bit,如果我们想保持输入输出的位宽是一致的,那就必须要进行移位。

在用FPGA做算法时,由于FPGA中一般都是使用定点数据,因此经常需要移位操作。比如一个16bit的信号经过滤波器后,由于滤波器的增益,输出结果肯定不是16bit,如果我们想保持输入输出的位宽是一致的,那就必须要进行移位。

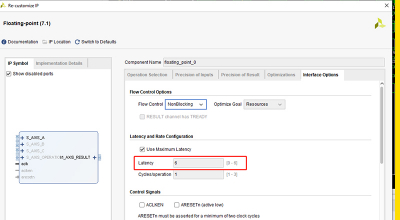

单片机的硬件串口,发送和接收完毕都有相应的标志位,例如TC(发送完成)和RXNE(接收完成)位。FPGA则不同,FPGA采用的是AXI4-Stream协议,数据送入IP核后,经过固定数量的时钟周期后,就得到运算结果,没有任何标志位表明运算完成。

DMA是直接内存访问(Direct Memory Access),DMA引擎可以将数据从一个地方传输到另一个地方,在传输过程中不经过CPU的控制。最简单的DMA用法是将数据从内存的一个区域搬运到另一个区域。

本文整理自Xilinx公开课:Vivado时序收敛技术。有些知识在公开课中讲的并不是很细,因此我又对齐进行了整理,分为了几篇文章。

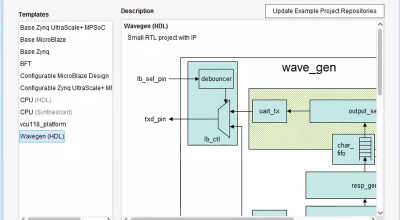

本篇文章我们以Vivado的wave_gen工程为例,来看下如何通过ECO来增加一个LUT,并对内部信号实现取反的功能。

Linux中USB驱动程序依然遵循标准的设备驱动模型——总线、设备、驱动。和I2C总线设备驱动一样,所有的USB驱动程序都必须创建的主要结构体是struct usb_driver,它们向USB核心代码描述了USB驱动程序,但这只是外壳,只实现了设备与总线的挂接,具体的USB设备是什么,如何实现,还需要编写相应的文件操作接口。本文详细介绍USB的驱动框架。

本文整理自Xilinx公开课:Vivado时序收敛技术。有些知识在公开课中讲的并不是很细,因此我又对齐进行了整理,分为了几篇文章。

本文对vivado、vitis、petalinux2021.1版本以及Vitis AI 1.4安装过程进行详细描述,并提供安装软件网盘地址。

通用串行总线(Universal Serial Bus)是连接计算机系统与外部设备的一种串行总线标准,也是一种输入输出接口的技术规范,被广泛地应用于个人电脑和移动设备等信息通信产品。USB总线是最复杂的总线之一,但其广泛使用。本文首先直接使用USB相关的驱动的应用,后面再具体开始编程做自己的USB驱动程序。

在百度edgeboard fzu3上运行CIFAR10 Classification,介绍Vitis AI TensorFlow设计过程,将Python描述的网络模型运行在Xilinx DPU上。