AD936x+ZYNQ搭建收音机(一)

judy 在 周二, 06/01/2021 - 09:38 提交

利用SDR做一个收音机是所有入门SDR都会做的小项目,简单直观易上手的特点和“Hello World”、流水灯一样。本篇文章就带领大家利用AD936X+ZYNQ平台SDR做个SDR。

利用SDR做一个收音机是所有入门SDR都会做的小项目,简单直观易上手的特点和“Hello World”、流水灯一样。本篇文章就带领大家利用AD936X+ZYNQ平台SDR做个SDR。

对于GP接口(general purpose)通用目的接口,有四个接口(两个从端口,两个主端口)。GP接口直接连接到的是中央互联区(central interconnect),然后由中央互联区再连接到OCM interconnect和存储器接口上。对于GP接口,通常使用他进行控制配置。

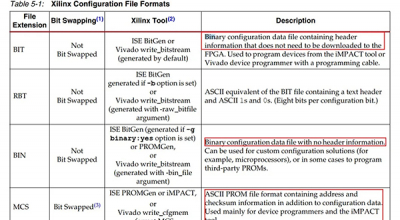

很多 FPGA 也是基于 SRAM 架构的,下载程序后运行,而断电后再次上电,需要重新下载程序。由此引出所谓的“固化”,即将程序下载到 EEPROM、Flash 等非易失性器件中,每次上电后从 EEPROM 或者 Flash 中加载对 FPGA 的配置(bitstream),比如 Xilinx FPGA 常用 QSPI Flash、SD 卡等方式。

今天给大侠带来Spartan-7 XC7S100程序固化 w25q128FVSG,解决xc7s不支持w25q系列芯片的问题,话不多说,上货。

FPGA里面的可执行文件都涉及到 *.bit, *.mcs, *.bin 和 *.elf,到底都有什么用,应该怎么用呢,这篇文章小编会简单介绍下这几种文件。

JTAG是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。现在多数的高级器件都支持JTAG协议,如DSP、FPGA器件等。标准的JTAG接口是4线:TMS(测试模式选择)、TCK(测试时钟输入)、TDI(测试数据输入)、TDO(测试数据输出)

fpga 上电时,默认是从 flash 的 0x00 地址开始读数据。如 UG470 文档 page144 描述

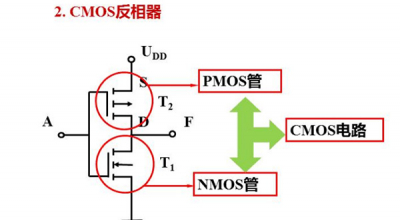

CMOS与非门,只要有一个输入端为低电平,与运算后均为低电平,输出为高电平,影响了输出结果,若接地或悬空会使输出始终为 1。CMOS与门、与非门:多余端通过限流电阻(500Ω)接电源;CMOS或门、或非门:多余端通过限流电阻(500Ω)接地;

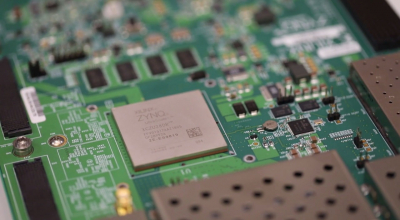

选择了xilinx zynq7z035ffg676这个型号的板子,是因为需要做定位通信的项目。AD9361+ZYNQ 的组合,因为需要自己一个人做PL和PS端的工作,这两部分的很多细节我都不了解,于是我向老板的一个专门做这块的朋友请教了我的一些问题,下面继续来整理一下。

依稀记得,当我第一次接触ZYNQ的时候,是在一个从零开始的项目中,可以说是需求都没确定,只是需要FPGA与ARM结合的平台,在迷茫的选择中,我选择了xilinx zynq7z035ffg676这个型号的板子