【Vitis指南】Xilinx Vitis 系列(四)

judy 在 周五, 04/16/2021 - 10:12 提交

今天带来第四篇,介绍使用Vitis IDE,包括Vitis命令选项和创建Vitis IDE项目。Vitis命令将使用您定义的选项启动Vitis IDE。它提供用于指定工作区的选项以及项目的选项。以下各节描述了Vitis命令的选项。

今天带来第四篇,介绍使用Vitis IDE,包括Vitis命令选项和创建Vitis IDE项目。Vitis命令将使用您定义的选项启动Vitis IDE。它提供用于指定工作区的选项以及项目的选项。以下各节描述了Vitis命令的选项。

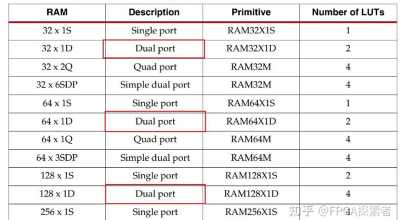

单口 RAM(Single RAM)、双口 RAM(Dual RAM)、简单双口 RAM(Simple-Dual RAM)、真双口 RAM(True-Dual RAM)有什么不同?对于 分布式 RAM,支持简单双口 RAM 和双口 RAM,不能配置成真双口 RAM。

今天带来第三篇,介绍使用Vitis分析仪。Vitis分析仪是一种实用工具,允许查看和分析,同时建立并运行应用程序生成的报告。旨在查看由构建应用程序时的Vitis编译器和运行应用程序时的Xilinx®Runtime(XRT)库生成的报告。

今天带来第一篇,介绍Vitis 2019.2软件平台发行说明、安装以及Vitis加速环境简介。

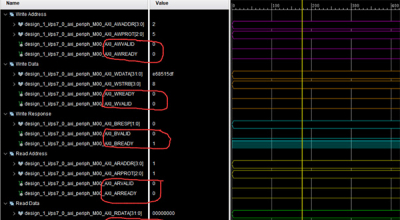

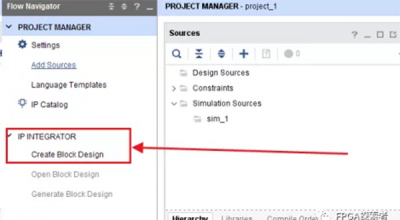

在 Vivado 中自定义 AXI4-Lite 接口的 IP,实现一个简单的 LED 控制功能,并将其挂载到 AXI Interconnect 总线互联结构上,通过 ZYNQ 主机控制,后面对 Xilinx 提供的整个 AXI4-Lite 源码进行分析。

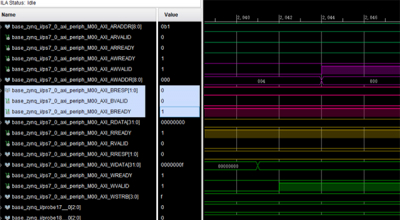

AXI4、AXI4-Lite和AXI4-Stream均使用Ready、Valid握手机制进行通信。信息传输的发起者使用Valid 信号指示数据何时有效,接收端产生 Ready 信号来表明已经准备好接收数据,当两者均为高时,启动传输。

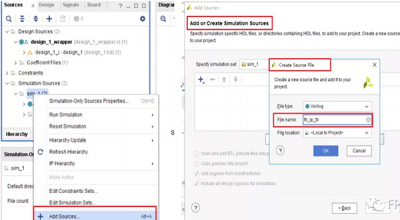

本讲使用两个 DDS 产生待滤波的信号和matlab产生带滤波信号,结合 FIR 滤波器搭建一个信号产生及滤波的系统,并编写 testbench 进行仿真分析,第五讲、第六讲开始编写 verilog 代码设计FIR滤波器,不再调用IP核。

本讲使用matlab产生待滤波信号,并编写testbench进行仿真分析,在Vivado中调用FIR滤波器的IP核进行滤波测试,下一讲使用两个DDS产生待滤波的信号,第五讲或第六讲开始编写verilog代码设计FIR滤波器,不再调用IP核。

TVM最大的特点是基于图和算符结构来优化指令生成,最大化硬件执行效率。其中使用了很多方法来改善硬件执行速度,包括算符融合、数据规划、基于机器学习的优化器等。它向上对接Tensorflow、Pytorch等深度学习框架,向下兼容GPU、CPU、ARM、TPU等硬件设备。

本讲在Vivado调用FIR滤波器的IP核,使用上一讲中的matlab滤波器参数设计FIR滤波器,下两讲使用两个DDS产生待滤波的信号和matlab产生带滤波信号,结合FIR滤波器搭建一个信号产生及滤波的系统,并编写testbench进行仿真分析