matlab与FPGA数字滤波器设计(1)——通过matlab的fdatool工具箱设计FIR数字滤波器

judy 在 周一, 03/29/2021 - 10:01 提交

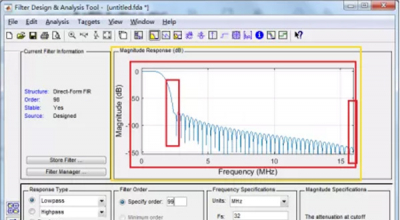

本文以99阶FIR低通滤波器为例,学习使用matlab的fdatool工具箱设计滤波器,并将滤波器系数导出到.coe文件,联合Vivado进行FPGA的FIR滤波器设计

本文以99阶FIR低通滤波器为例,学习使用matlab的fdatool工具箱设计滤波器,并将滤波器系数导出到.coe文件,联合Vivado进行FPGA的FIR滤波器设计

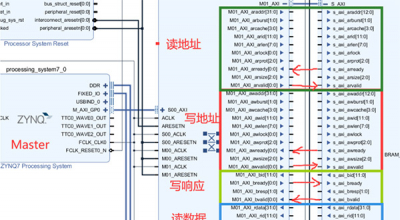

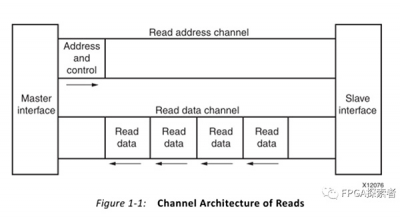

AXI4协议是一个点对点的主从接口协议,数据可以同时在主机(Master)和从机(Slave)之间双向传输,且数据传输大小可以不同。AXI4中的限制是一个突发事务(Burst)最多可以传输256个数据,AXI4-Lite只允许每个事务传输1个数据。

AMBA® AXI4(高级可扩展接口 4)是 ARM® 推出的第四代 AMBA 接口规范,AMBA(Advanced Microcontroller Bus Architecture)是片上总线标准,包含AHB(Advanced High-performance Bus)、ASB(Advanced System Bus)和 APB(Advanced Peripheral Bus)。

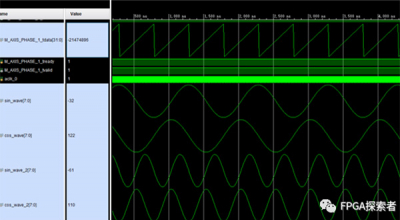

本次使用Vivado调用DDS的IP进行仿真,并尝试多种配置方式的区别,设计单通道信号发生器(固定频率)、Verilog查表法实现DDS、AM调制解调、DSB调制解调、可编程控制的信号发生器(调频调相)。

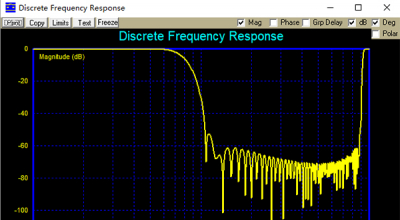

我们上一篇文章的混频是8MHz与5MHz的相乘,所以我们这篇文章的目的是设计一个低通滤波器滤除13MHz的成分。FIR的设计方法在数字信号处理中有两种方法,最常用的就是窗函数法。这里我们将使用汉明窗进行进一步的设计。

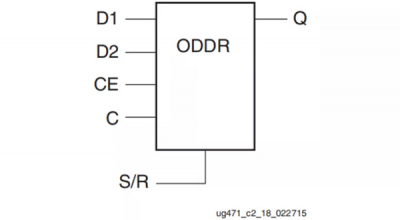

本文探讨一下ODDR用于时钟输出时的作用。

IBERT(Integrated Bit ErrorRatio Tester,集成误比特率测试工具),是Xilinx提供用于调试FPGA高速串行接口比特误码率性能的工具,最常用在GT高速串行收发器测试:

(1)基于PRBS模块的误码率测试;

(2)测量眼图;

ZC706中,MAC 控制器与 PHY 通过 RGMII(Reduced Gigabit Media Independent Interface)接口进行连接,实现千兆网。

在Vivado使用过程中,会碰到如下情况:设计代码已经编写完成,且仿真、综合或实现中的某一步骤已经通过,不需要再修改。此时可能需要添加一些注释代码,或者调整代码的格式,而任何修改都会导致状态更改为“Out of date”,提示用户更新设计。如何才能在不重新运行综合或实现的情况下解决这个问题?

针对异步复位、同步释放,一直没搞明白在使用同步化以后的复位信号时,到底是使用同步复位还是异步复位?比如针对输入的异步复位信号rst,使用本地时钟clk将其同步化以后得到一个新的复位信号sys_rst,当使用sys_rst时,是将sys_rst作为同步复位信号还是异步复位信号?