Vivado版本升级导致的IP锁定的更新解决办法

judy 在 周四, 03/04/2021 - 11:58 提交

vivado建立的工程经常会出现版本升级而导致的IP核锁定情况,本文以vivado 2019.2的版本打开旧版本为例,介绍两种更新方法

vivado建立的工程经常会出现版本升级而导致的IP核锁定情况,本文以vivado 2019.2的版本打开旧版本为例,介绍两种更新方法

总结了20个DDR3和FPGA部分的设计规范

在Xilinx FPGA中实现的设计不需要插入全局复位网络。对于绝大多数设计,所有触发器和RAM的上电后的初始化状态比任何的逻辑复位都要全面,不需要为了仿真而插入复位,因为没有任何东西是未定义的

FPGA 融合了 ASIC 和基于处理器的系统的最大优势,它能够提供硬件定时的速度和稳定性,且无需类似自定制 ASIC 设计的巨额前期费用的大规模投入。但是和所有的数字电路一样,FPGA 电路中也存在毛刺问题。它的出现会影响电路工作的可靠性、稳定性,严重时会导致整个数字系统的误动作和逻辑紊乱。下面就来讨论交流一下FPGA 的竞争冒险与毛刺问题。

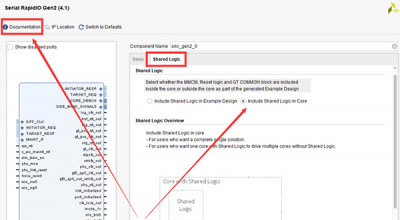

这里以Xilinx为例,在Vivado中使用SRIO高速串行协议的IP演示如何使用官方例程和手册进行快速使用,在仔细阅读参考官方例程后进行一些修改就可以应用在实际项目中。

源语(Primitives)-Xilinx库中最简单的设计元素。Primitives 基元是设计元素“原子”。Xilinx原语的示例包括简单缓冲区BUF和带有时钟使能和清除功能的D触发器FDCE。

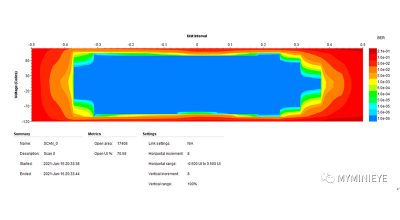

IBERT(集成误码率测试仪)是xilinx为7系列FPGA GTX收发器设计的,用于评估和监控GTX收发器。IBERT包括在FPGA逻辑中实现的模式生成器和检查器,以及对端口的访问和GTX收发器的动态重新配置端口属性,还包括通信逻辑,以允许设计在运行时通过JTAG进行访问。IBERT工具用于对Xilinx FPGA芯片的高速串行收发器进行板级硬件测试。

都知道FPGA的启动方式有很多种,比如JTAG、SPI,BPI,SeletMAP,Serial等等吧,又分为主从即Master和Slave(时钟由FPGA的管脚发出,专用的CCLK信号为主,否则为从,有的配置有辅助时钟EMCCLK,它由外部的晶振提供,从FPGA的EMCCLK输入,经过专用的逻辑,再从CCLK管脚输出给想用的器件,),那么问题来了,配置失败怎么办呢??????????????

所谓增量实现,更严格地讲是增量布局和增量布线。它是在设计改动较小的情形下参考原始设计的布局、布线结果,将其中未改动的模块、引脚和网线等直接复用,而对发生改变的部分重新布局、布线。这样做的好处是显而易见的,即节省运行时间,能提高再次布局、布线结果的可预测性,并有助于时序收敛。

使用Vivado Runs基础结构时(例如,launch_runs Tcl命令),请将此命令添加到.tcl文件,并将该文件作为执行运行的write_bitstream步骤的预钩添加