Xilinx源语-------FDRE

judy 在 周五, 11/27/2020 - 15:54 提交

FDRE代表一个单D型触发器,含的有五个信号分别为: 数据(data,D)、时钟使能(Clock enable,CE)、时钟(Clock)、同步复位(synchronous reset,R)、数据输出(dataout,Q)。当输入的同步复位信号为高时,否决(override)所有输入,并在时钟的上升沿将输出Q为低信号。

FDRE代表一个单D型触发器,含的有五个信号分别为: 数据(data,D)、时钟使能(Clock enable,CE)、时钟(Clock)、同步复位(synchronous reset,R)、数据输出(dataout,Q)。当输入的同步复位信号为高时,否决(override)所有输入,并在时钟的上升沿将输出Q为低信号。

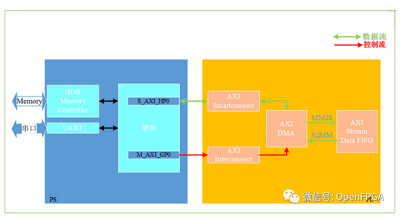

增加一个AXIDMA章节,这部分内容是很多例程的基础,难度不大但是也不小,需要彻底理解整个运行机制。

有的时候需要查找一些官网的例程进行学习和参考,但是总感觉无从下手,今天就教大家怎么利用官网和Vivado的Documention进行相关的操作。

ZYNQ-7000系列MIO/EMIO/AXI_GPIO接口

区别于传统的一根信号线一根地线的做法,差分传输在两根线上都传输信号,这两个信号的振幅相同,相位相反,在这两根线上的传输的信号就是差分信号。信号接收端通过比较这两个电压的差值来判断发送端发送的逻辑状态。在电路板上,差分走线必须是等长、等宽、紧密靠近、且在同一层面的两根线。

AXI4-Stream跟AXI4的区别在于AXI4-Stream没有ADDR接口,这样就不涉及读写数据的概念了,只有简单的发送与接收说法,减少了延时,允许无限制的数据突发传输规模。AXI4-Stream的核心思想在于流式处理数据。

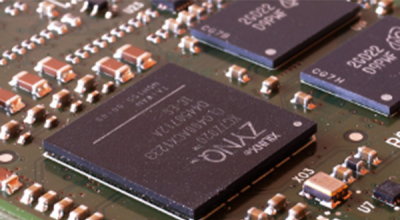

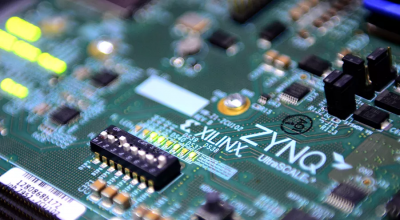

随着赛灵思公司推出28nm Zynq-7000 All Programmable SoC以后,FPGA在工业应用大有加速之势,赛灵思工业级客户增长非常迅猛,其数量远超通信客户。赛灵思Zynq器件在智能化工业自动化领域大显身手,它将给工业应用带来哪些深刻变革?

在《AXI-Lite 自定义IP》章节基础上,添加ila\vio等调试ip,完成后的BD如下图:加载到SDK,并且在Vivado中连接到开发板。

Trigger Setup,点击“+”,选择 AXI_WVALID,双击添加。设置 Radix 为 B,触发条件 Value 为 1。

最近群里有很多人遇到上述的情况,一直觉得不可思议,以前没有遇到这种情况,如果是很常见的情况,那官网一定有人反馈,如果是极特别的情况,那么也就只能按照BUG处理了。很幸运,官网有很多人反馈类似的问题,先把问题和解决方式放出来:

FPGA (Field Programmable Gate Aray,现场可编程门阵列)是一种可通过重新编程来实现用户所需逻辑电路的半导体器件。为了便于大家理解FPGA的设计和结构,我们先来简要介绍一些逻辑电路的基础知识。