ZYNQ Linux开发——ZedBoard使用ubuntu16.04文件系统+桌面

judy 在 周六, 12/29/2018 - 10:19 提交

文件系统用的Koheron提供的ubuntu16.04,将镜像文件解压后可以直接使用文件系统,具体使用命令的命令是fdisk 和mount

文件系统用的Koheron提供的ubuntu16.04,将镜像文件解压后可以直接使用文件系统,具体使用命令的命令是fdisk 和mount

本文主要介绍一些常见的PCIe设计方案,针对PCIe接口的PCB设计。

FPGA挂载SATA SSD需要SATA IP,IP报价动辄十几W,开源的IP也有,但都是基于V6或者V5等老器件的。现在好了,NVME SSD大行其道,而且不需要IP,可以说为广大爱好者带来的福音

私有定时器属于PS部分,定时器可以帮我们计数、计时,有效的控制模块的时序。这一次实验我们认识定时器并使用定时器产生中断。

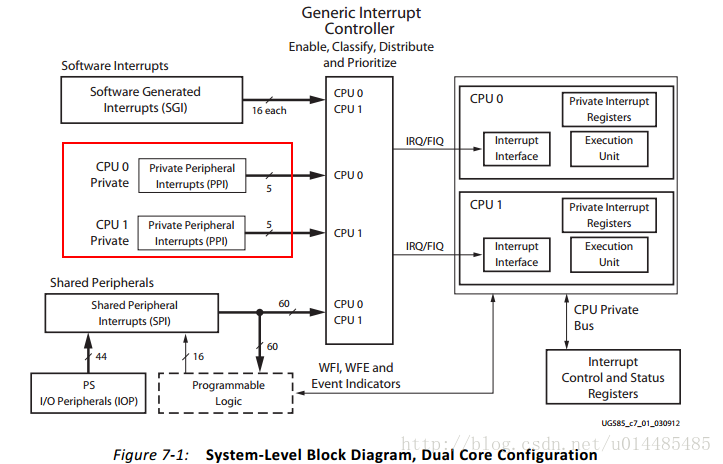

CPU的私有中断(PPI),5个:全局定时器, 私有看门狗定时器, 私有定时器以及来自 PL 的 FIQ/IRQ。

它们的触发类型都是固定不变的, 并且来自 PL 的快速中断信号 FIQ 和中断信号 IRQ 反向, 然后送到中断控制器因此尽管在ICDICFR1 寄存器内反映的他们是低电平触发,但是 PS-PL 接口中为高电平触发。

CPU的私有定时器:每个CPU都有自己的私有定时器:

私有定时器的工作频率是CPU的一半(频率仅供参考,主要看频率分配比率):

System Generator是Xilinx公司进行数字信号处理开发的一种设计工具,它通过将Xilinx开发的一些模块嵌入到Simulink的库中,可以在Simulink中进行定点仿真,可以设置定点信号的类型,这样就可以比较定点仿真与浮点仿真的区别。并且可以生成HDL文件,或者网表,可以在ISE中进行调用

Zynq系列FPGA分为PS部分和PL部分。

PL: 可编程逻辑 (Progarmmable Logic), 就是FPGA部分。

PS: 处理系统 (Processing System) , 就是与FPGA无关的ARM的SOC的部分,实质是直接操作arm9内核的处理器。

这次先是最简单地在PL部分编写一个流水灯实验的代码。

使用的开发环境是vivado 2016.4。

1、新建工程,Create New Project。

2、next。

3、选择工程目录,和输入工程名字。

PS和PL之间的交互,怎么都逃不过中断,稍微大型的数字系统,PS和PL之间配合使用就需要中断作为桥梁。本文通过按键发起中断请求尝试学习PL请求中断的处理机制。

环境准备

首先肯定是要下载xilinx-2011.09-50-arm-xilinx-linux-gnueabi.bin文件,这是官方提供的linux下交叉编译链安装文件,下载地址为:https://pan.baidu.com/s/1eSP85nO 。

安装交叉编译环境工作:

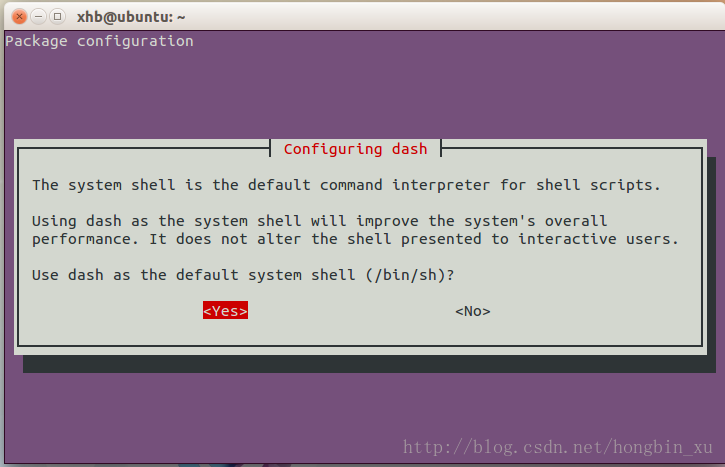

1、由于安装文件只能在bash下运行,所以要将dash改为bash,输入以下指令:

sudo dpkg-reconfigure -plow dash

选择No,切换到bash。

2、建立一个文件夹作为安装路径;

我的指定的安装目录为:/opt/cross_compiler

System Generator是Xilinx公司进行数字信号处理开发的一种设计工具,它通过将Xilinx开发的一些模块嵌入到Simulink的库中,可以在Simulink中进行定点仿真,可以设置定点信号的类型,这样就可以比较定点仿真与浮点仿真的区别。并且可以生成HDL文件,或者网表,可以在ISE中进行调用

Block RAM是PL部分的存储器阵列,为了与DRAM(分布式RAM)区分开,所以叫块RAM。ZYNQ的每一个BRAM 36KB,7020的BRAM有140个(4.9M),7030有265个(9.3M),7045有545个(19.2M)。每一个BRAM都有两个共享数据的独立端口,当然是可以配置的,可用于片内数据缓存、FIFO缓冲