ZYNQ+Vivado2015.2系列(十五)AXI Timer 用户定时器中断控制LED

judy 在 周一, 01/21/2019 - 09:47 提交

前面的中断学习中我们学了按键,GPIO,Timer,是时候把它们整合到一起了。今天我们混合使用PS/PL部分的资源,建立一个比较大的系统

前面的中断学习中我们学了按键,GPIO,Timer,是时候把它们整合到一起了。今天我们混合使用PS/PL部分的资源,建立一个比较大的系统

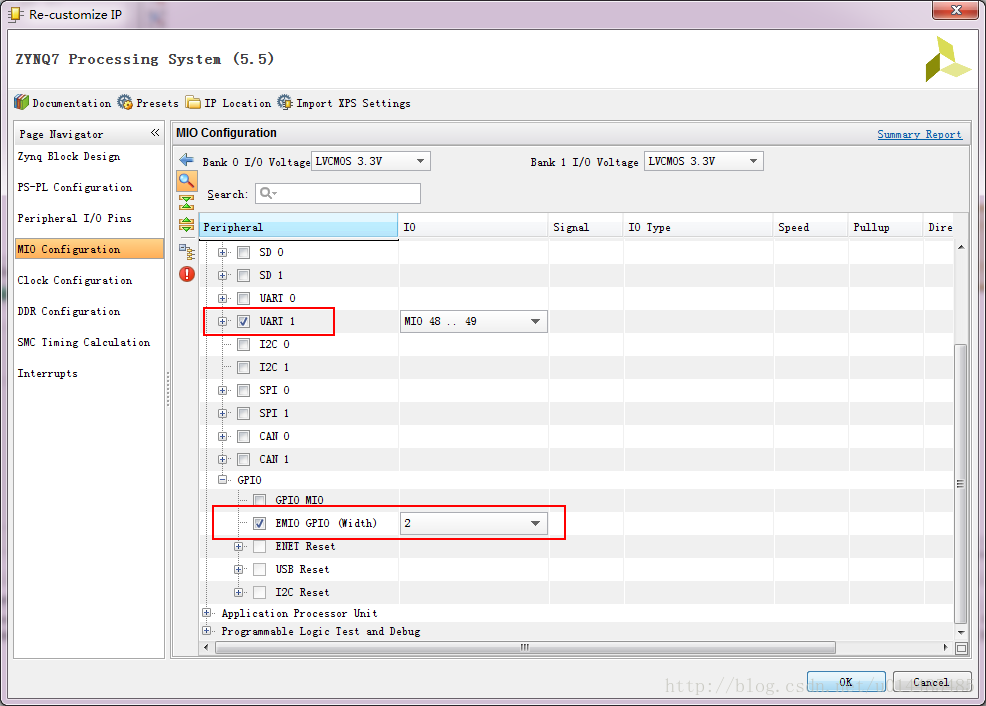

Zynq7000 系列芯片有 54 个 MIO(multiuse I/O), 它们分配在 GPIO 的 Bank0 和Bank1 隶属于 PS 部分, 这些 IO 与 PS 直接相连。 不需要添加引脚约束, MIO 信号对 PL部分是透明的。 所以对 MIO 的操作可以看作是纯PS 的操作

ug948中提供的官方例程为图像的中值滤波,该设计将一副256*256大小的RGB图像,添加噪声后提取出其中的Y通道,使用C++语言完成中值滤波。该设计将在Simulink环境下进行仿真。本次设计的流程是利用Vivado HLS建立C/C++代码,Export RTL–>System Generator–>Vivado

Zynq最核心的设计理念就是软件加硬件,即PS+PL。通过软硬件协同设计,结合了FPGA与双arm9内核,对于嵌入式拥有极大的优势。整个片上系统主要使用资源:ZYNQ系列FPGA XC7Z020、2片DDR、串口芯片(USB转UART)。Zedboard板子自带了这些资源,不需要另外添加模块。

System Generator是Xilinx公司进行数字信号处理开发的一种设计工具,它通过将Xilinx开发的一些模块嵌入到Simulink的库中,可以在Simulink中进行定点仿真,可以设置定点信号的类型,这样就可以比较定点仿真与浮点仿真的区别。并且可以生成HDL文件,或者网表,可以在ISE中进行调用。或者直接生成比特流下载文件。能够加快DSP系统的开发进度。

一、Black Box调用HDL代码

1、简介

System Generator提供了一个特性:可以通过black box这个block将其它HDL文件以黑盒的形式封装到System Generator设计中,在仿真时使用Simulink+Vivado Simulator(或ModelSim)协同仿真的方法,在Simulink环境中完成设计的仿真测试。

具体介绍大家可以查阅相关资料。

2、本部分设计使用到的block

Xilinx block

其它block

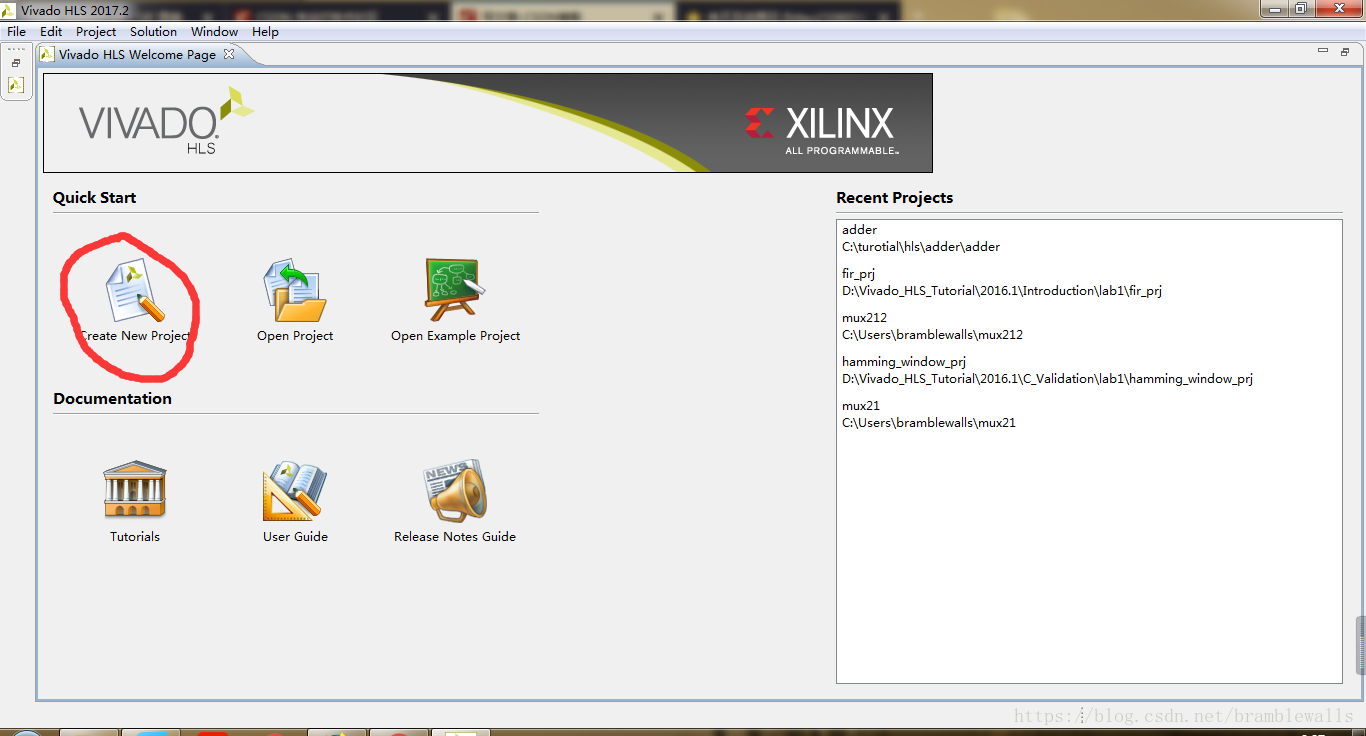

一、用HLS生成一个定制IP(加速器)

(1)首先打开vivado hls,本人的版本是2017.2,点击创建一个新工程。

(2)设置工程名和路径,顶层函数设置为add,创建一个新的C++程序,名字叫做adder.cpp,不用在testbench中添加文件。

选择板子的时候搜索xc7z020clg400-1,这是PYNQ的板子号,选择完成。

前面我们介绍了按键中断,其实我们稍作修改就可以用按键控制LED了。做个小实验,两个按键分别控制两个led亮灭。

板子:zc702。

硬件部分

添加zynq核:

勾选串口用于打印信息,勾选EMIO,我们控制两个led,所以需要2bit

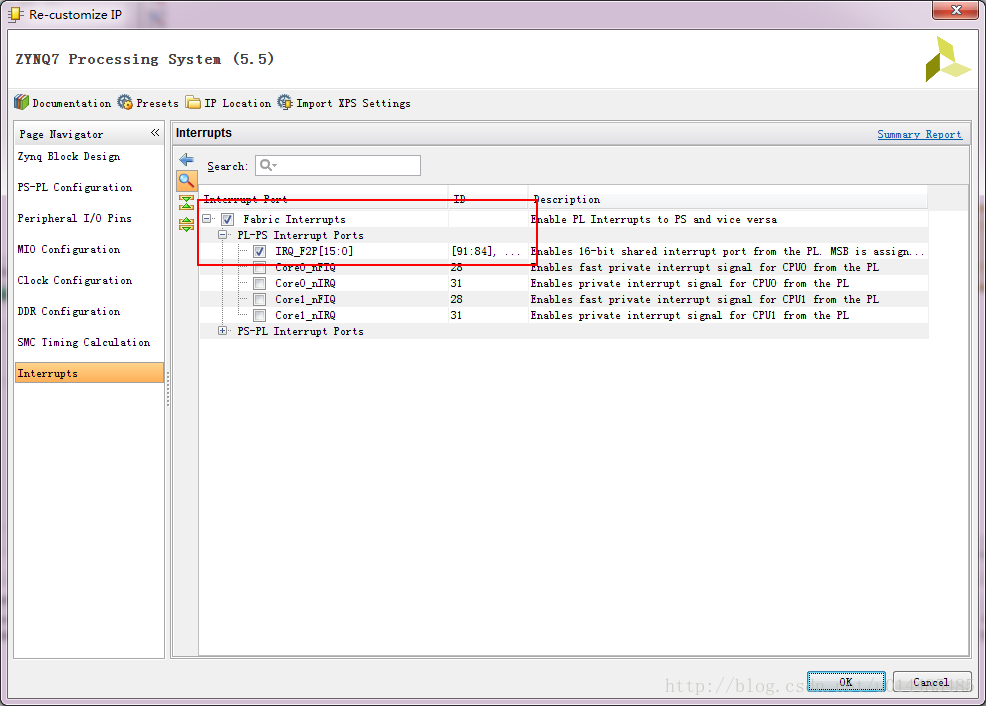

PL 到PS的中断勾选上:

PL时钟什么的都用不到,我们用的按键不需要时钟,EMIO属于PS。

再添加一个concat IP用于合并两路按键信号:

FPGA设计中经常用到一些控制逻辑,如有限状态机(FSM),如果用各种block搭建一个FSM比较麻烦。System Generator支持调用MATLAB代码,通常可以编写MATLAB代码来实现FSM等控制逻辑,通过MCode block调用到System Generator设计中。

1. 首先要在Ubuntu下安装Petalinux 2017.2

2. 设置Petalinux 环境变量

source /

3. 新建目录~/projets/fpga-drive-aximm-pcie

4. 把Windows下的Vivado工程复制到~/projets/fpga-drive-aximm-pcie下

5. 新建Petalinux工程

petalinux-create --type project --template zynq --name petalinux_prj

6. 切换到petalinux_prj目录

cd petalinux_prj/

7. 导入HDF

petalinux-config --get-hw-description ../fpga-drive-aximm-pcie-2017v2_hpc/Vivado/zc706_hpc_pcie/zc706_hpc_pcie.sdk/

随之弹出Linux System Configuration界面,不做任何更改,保存退出

Simulink中的仿真模型为连续时间系统,数据格式多种多样;而FPGA中为离散时间系统,数据必须用一定的位数进行量化。两者之间必须要进行从连续到离散的转换、数据格式的转换,否则无法进行正确的FPGA设计