基于FPGA的数字信号处理(1)--一文搞懂定点数

judy 在 周二, 09/03/2024 - 15:15 提交

数字电路中,小数可以用两种形式来表示:「定点数」和「浮点数」。浮点数的内容我们下篇文章再讲,本文只讲定点数。

数字电路中,小数可以用两种形式来表示:「定点数」和「浮点数」。浮点数的内容我们下篇文章再讲,本文只讲定点数。

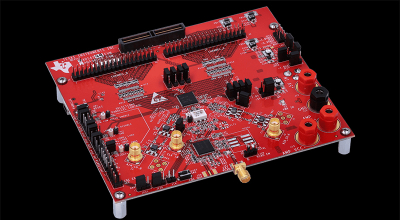

本文以TI的ADS4249(ADC)和DAC3482(DAC)之间的接口为例,介绍Altera FPGA与ADC/DAC之间的DDR LVDS接口设计以及时序约束详细设计。

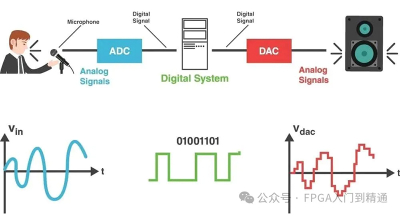

今天,我们将一起探索数字信号处理基础中至关重要的两个概念:连续信号离散化与采样定理。

本文描述了ADC和FPGA之间LVDS接口设计需要考虑的因素,包括LVDS数据标准、LVDS接口数据时序违例解决方法以及硬件设计要点

本文介绍了基于XILINX FPGA的米联客UDP协议栈的实现原理、内部逻辑、仿真测试、上板验证

本文将以通俗易懂的方式,让大家深入了解数字信号处理基础中的时域概念。

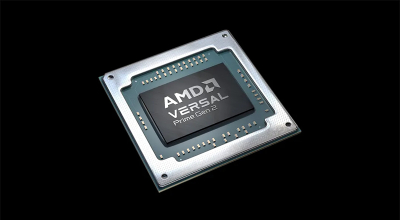

随着数据量的爆炸性增长和计算需求的多样化,传统的“一刀切”式CPU已经难以满足所有应用的需求

在数字信号处理的奇妙世界里!“信号”是一切的基础,理解了信号,就相当于拿到了开启数字信号处理大门的钥匙。

本文介绍FPGA与高速ADC接口方式和标准以及JESD204与FPGA高速串行接口。