Xilinx原语详解及仿真——ODELAYE2

judy 在 周一, 12/09/2024 - 17:52 提交

7系列IO模块相关的结构如图1所示,前文对IOB、IDELAYE2、ILOGIC、OLOGIC进行了讲解,还剩下ISERDESE2、OSERDESE2、ODELAYE2原语

7系列IO模块相关的结构如图1所示,前文对IOB、IDELAYE2、ILOGIC、OLOGIC进行了讲解,还剩下ISERDESE2、OSERDESE2、ODELAYE2原语

本次项目展示了如何创建 CLI 来控制机械臂的 PWM 驱动器。还创建了一个详细的 Python 应用程序,该应用程序与 AMD MicroBlaze™ V 配合使用

以下是您需要了解的有关这些尖端半导体的所有信息,随着全球对人工智能的狂热,它们的需求也飙升。

SDRAM具有空间存储量大、读写速度快、价格相对便宜等优点。然而由于SDRAM内部利用电容来存储数据,为保证数据不丢失,需要持续对各存储电容进行刷新操作

常规的外差式无线电接收器已经使用了近一个世纪,如图所示。我们再次回顾一下模拟接收器的结构,以便于和数字接收器进行比较

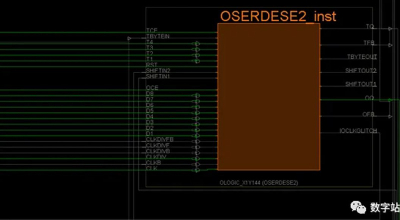

OSERDESE2是7系列FPGA器件中的专用并串转换器,具有特定的时钟和逻辑资源

Xilinx 的开发工具Vivado其实还是比较好上手的,在左边的设计流程导航已经把FPGA的开发过程按先后顺序给排列出来了

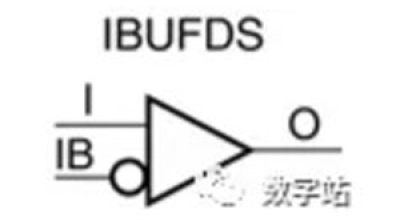

在使用FPGA时,往往会用到一些差分信号,比如HDMI接口,LVDS接口的ADC、显示器等等设备,而FPGA内部往往只会使用单端信号

之前介绍过使用RP2040制作逻辑分析仪及示波器,今天我们使用FPGA搭建逻辑分析仪

`timescale指令我相信大家应该都不陌生,或多或少都见过,可能绝大部分人都能运用,但其实这个常用指令用起来还是有一些需要注意的