使用 IP 核和开源库减少 FPGA 设计周期

judy 在 周一, 01/06/2025 - 16:27 提交

很多FPGA厂商都在自己EDA工具里嵌入IP减少FPGA项目的开发周期,使用 IP 是一种有助于实现按时、高质量且经济高效的项目交付的方法

很多FPGA厂商都在自己EDA工具里嵌入IP减少FPGA项目的开发周期,使用 IP 是一种有助于实现按时、高质量且经济高效的项目交付的方法

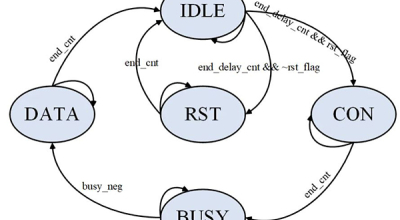

前文讲解了AD7606的功能及原理,本文通过FPGA实现AD7606的并行接口数据采集,对应时序如下所示

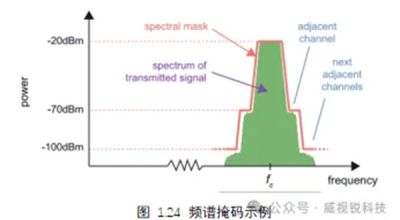

脉冲包含所有频率,通过无线电信道传输脉冲将产生带宽极宽的无线电信号,这些信号会侵入相邻频带,对其他用户造成干扰。

WM8731是集成耳机驱动器的低功耗立体声编解码器,有2路24位的ADC及DAC,支持16~32位的数字音频输入字长和8kHz~96kHz的采样速率

本文介绍PCIe IP核时钟结构、PCIe板卡时钟方案及复位设计相关内容。

本文将详细介绍图像镜像算法的基本原理、Python实现以及FPGA实现。

在 FPGA 上实现延时定时(Delay Timing)通常需要根据实际需求选择高效的方法,以下是两种常见且高效的实现方法

为保证FPGA设备可以连接并被系统识别,本节讨论了PCIe基础规范和PCIe板卡电气规范的对FPGA配置时间具体要求。

本文旨在回顾通过部署现场可编程门阵列(FPGA 设备)来提高数据中心 operational 效率的方法

AD7606是ADI的一款8通道16位同步采样的ADC芯片,最大采样率可以得到200KSPS,模拟输入电压范围最大可以选择±5V或者±10V