在 FPGA 上实现延时定时(Delay Timing)通常需要根据实际需求选择高效的方法,以下是两种常见且高效的实现方法:

1. 使用硬件计数器(Counter)

计数器是实现延时定时最常见的方法,通过时钟信号驱动计数器,按需生成延时。

工作原理

使用 FPGA 的全局时钟(如 50 MHz 或 100 MHz)作为计数器的输入。

根据需要的延时时间计算计数器的计数值。

当计数器达到目标值时,输出信号触发。

实现步骤

设定计数值:

例如,1ms 延时在 50 MHz 时钟下需要计数 50,000。

设定延时时间T 和时钟频率,计算计数值:

例如,1ms 延时在 50 MHz 时钟下需要计数 50,000。

编写 Verilog/VHDL 代码:

module delay_counter( input wire clk, input wire rst, output reg delay_done ); parameter TARGET_COUNT = 50000; reg [15:0] counter = 0; always @(posedge clk or posedge rst) begin if (rst) begin counter <= 0; delay_done <= 0; end else if (counter < TARGET_COUNT) begin counter <= counter + 1; delay_done <= 0; end else begin delay_done <= 1; end end endmodule

优点

易于实现,适用于固定延时。

使用较少的逻辑资源。

缺点

随着延时增加,计数器位宽会增大。

2. 使用 FPGA 的硬件计时器(Timer)

大多数现代 FPGA 提供硬件计时器 IP 核,可以高效实现定时。

工作原理

利用 FPGA 内置的计时器模块,例如 Xilinx 的 AXI Timer 或 Intel 的 Timer IP。

通过配置定时器参数生成精确的延时信号。

实现步骤

配置硬件计时器:

使用厂商提供的 FPGA 开发工具(如 Vivado 或 Quartus)配置计时器 IP。

设置定时器的计数值或定时周期。

使用定时器控制逻辑:

通过寄存器接口启动定时器。

等待定时器完成计时后,生成中断或触发信号。

优点

减少手动设计工作量。

提供更高的计时精度,支持动态修改延时时间。

缺点

需要使用厂商工具配置 IP,稍显复杂。

对资源有限的小型 FPGA,可能会增加额外的开销。

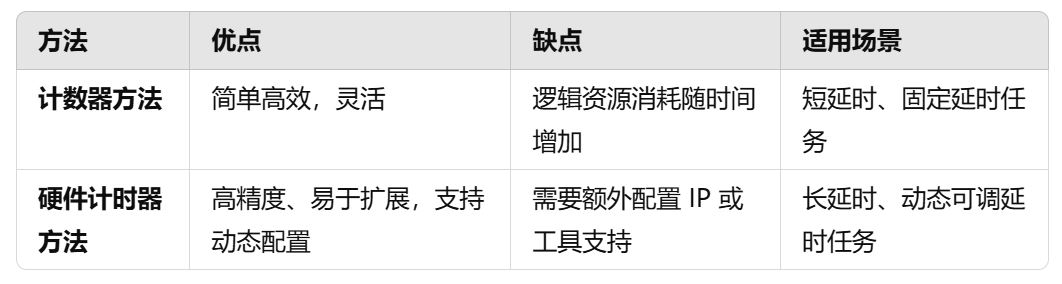

对比总结

根据应用场景选择合适的延时实现方式,可以显著提高 FPGA 的设计效率和资源利用率。