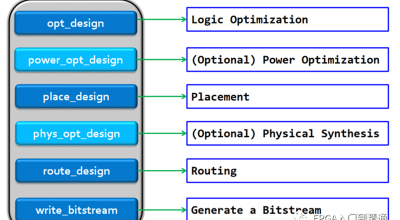

Vivado布线和生成bit参数设置

judy 在 周四, 09/14/2023 - 09:29 提交

本文主要介绍Vivado布线参数设置

本文主要介绍Vivado布线参数设置

AMD 128核心/256线程EPYC 9754处理器独家测试

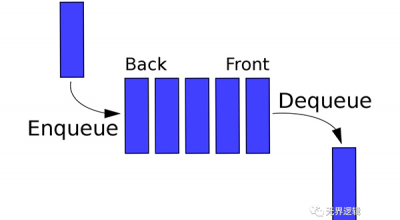

异步FIFO通常用于跨时钟域处理,是逻辑设计常用基础模块

本文将介绍Vivado增量编译的基本概念、优点、使用方法以及注意事项

查看MIG IP输出的init_calib_complete信号

FIFO:First in, first out,先进先出;其主要作用是:数据缓存

内置校准: DDR3和DDR4控制器通常具有内置的校准机制

本文主要是记录MAC在RGMII接口中的设计。

Vivado综合工具支持多种属性设置,可以在RTL文件或XDC文件中进行设

本文将介绍如何在FPGA上快速搭建以太网