Xilinx DDR3学习总结——1、MIG核设置

judy 在 周五, 09/08/2023 - 10:48 提交

话说之前从来没有使用过DDR,工作中的项目都是流式处理的

话说之前从来没有使用过DDR,工作中的项目都是流式处理的

本文将介绍Vivado综合工具支持的常用属性设置,并给出了Verilog示例

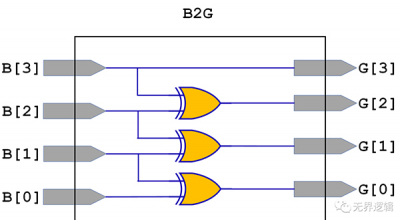

格雷码是一种反射二进制码编码方式

本文将介绍Vivado综合工具支持的常用属性设置

本文介绍如何通过XPM调用URAM,并让级联URAM获得最佳时序性能

我们知道以太网的通信离不开PHY芯片,那PHY和RGMII接口到底是什么关系呢?

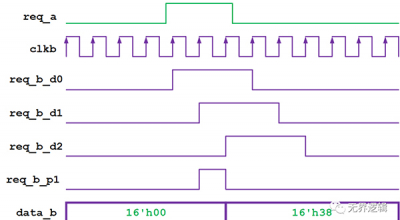

多bit信号跨时钟域的处理方法之一是握手法,也可以称作应答法

本项目将是一个非常简化的基带符号映射器,用于 FSK 数字调制方案的链的发送端

本文介绍Vivado中如何进行FPGA设计资源优化以及查看各子模块资源占用的方法

本文介绍PCIe引脚定义以及PCIe协议层